The following document contains information on Cypress products. Although the document is marked with the name "Spansion" and "Fujitsu", the company that originally developed the specification, Cypress will continue to offer these products to new and existing customers.

### **Continuity of Specifications**

There is no change to this document as a result of offering the device as a Cypress product. Any changes that have been made are the result of normal document improvements and are noted in the document history page, where supported. Future revisions will occur when appropriate, and changes will be noted in a document history page.

### **Continuity of Ordering Part Numbers**

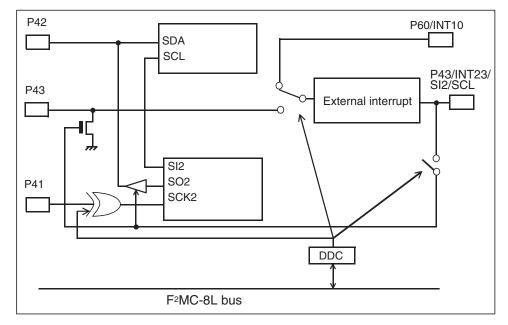

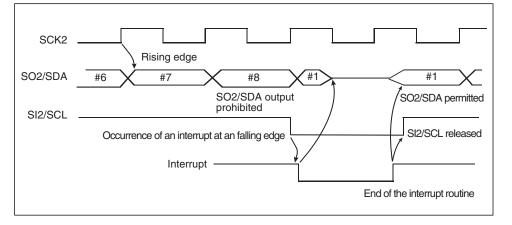

Cypress continues to support existing part numbers. To order these products, please use only the Ordering Part Numbers listed in this document.

### For More Information

Please contact your local sales office for additional information about Cypress products and solutions.

### **About Cypress**

Cypress (NASDAQ: CY) delivers high-performance, high-quality solutions at the heart of today's most advanced embedded systems, from automotive, industrial and networking platforms to highly interactive consumer and mobile devices. With a broad, differentiated product portfolio that includes NOR flash memories, F-RAM<sup>™</sup> and SRAM, Traveo<sup>™</sup> microcontrollers, the industry's only PSoC<sup>®</sup> programmable system-on-chip solutions, analog and PMIC Power Management ICs, CapSense<sup>®</sup> capacitive touch-sensing controllers, and Wireless BLE Bluetooth<sup>®</sup> Low-Energy and USB connectivity solutions, Cypress is committed to providing its customers worldwide with consistent innovation, best-in-class support and exceptional system value.

**FUJITSU SEMICONDUCTOR**

CONTROLLER MANUAL

# F<sup>2</sup>MC-8L 8-BIT MICROCONTROLLER MB89530/530H/530A Series HARDWARE MANUAL

# F<sup>2</sup>MC-8L 8-BIT MICROCONTROLLER MB89530/530H/530A Series HARDWARE MANUAL

**FUJITSU LIMITED**

### Objectives and Intended Readers

Thank you for purchasing Fujitsu semiconductor products.

The MB89530/530H/530A series of microcontrollers was developed as a general-purpose product in the  $F^2MC$  ( $\otimes^*$ -8L series that comprises the proprietary 8-bit one-chip microcontroller that supports application specific ICs (ASICs). This product is designed for a broad range of uses, from consumer products to industrial equipment, such as portable devices.

This manual describes the functions and operations of the MB89530/530H/530A series of microcontrollers for engineers who develop products using this series. Be sure to read this manual thoroughly.

For details on the instructions, see the F<sup>2</sup>MC Programming Manual.

### Trademark

F<sup>2</sup>MC, an abbreviation for FUJITSU Flexible Microcontroller, is a registered trademark of Fujitsu Limited.

### Organization of this manual

This manual consists of the following 23 chapters and appendix:

### **CHAPTER 1 "OVERVIEW"**

This chapter explains the features and basic specifications of the MB89530/530H/530A series of microcontrollers.

#### CHAPTER 2 "HANDLING DEVICE"

This chapter describes the precautions to be taken when using the MB89530/530H/530A series of microcontrollers.

### CHAPTER 3 "CPU"

This chapter describes the functions and operations of the CPU.

### CHAPTER 4 "I/O PORTS"

This chapter describes the functions and operations of the I/O port.

### CHAPTER 5 "TIMEBASE TIMER"

This chapter describes the functions and operations of the timebase timer.

### CHAPTER 6 "WATCHDOG TIMER"

This chapter describes the functions and operations of the watchdog timer.

#### CHAPTER 7 "WATCH PRESCALER"

This chapter describes the functions and operations of the watch prescaler.

### CHAPTER 8 "2-CHANNEL 8-BIT PWM TIMERS"

This chapter describes the functions and operations of the 2-channel 8-bit PWM timer.

### CHAPTER 9 "PULSE-WIDTH COUNT TIMER (PWC)"

This chapter describes the functions and operations of the pulse width count timer (PWC).

### CHAPTER 10 "6-BIT PPG TIMER"

This chapter describes the functions and operations of 6-bit PPG timer.

### CHAPTER 11 "12-BIT PPG TIMER"

This chapter describes the functions and operations of the 12-bit PPG timer.

### CHAPTER 12 "16-BIT TIMER/COUNTER"

This chapter describes the functions and operations of the 16-bit timer/counter.

### CHAPTER 13 "EXTERNAL INTERRUPT CIRCUIT 1 (EDGE)"

This chapter describes the functions and operations of external interrupt circuit 1 (edge).

### CHAPTER 14 "EXTERNAL INTERRUPT CIRCUIT 2 (LEVEL)"

This chapter describes the functions and operations of external interrupt circuit 2 (level).

### CHAPTER 15 "A/D CONVERTER"

This chapter describes the functions and operations of the A/D converter.

#### CHAPTER 16 "UART/SIO"

This chapter describes the functions and operations of the UART/SIO.

### CHAPTER 17 "HIGH-SPEED UART"

This chapter describes the functions and operations of the high-speed UART.

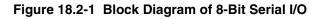

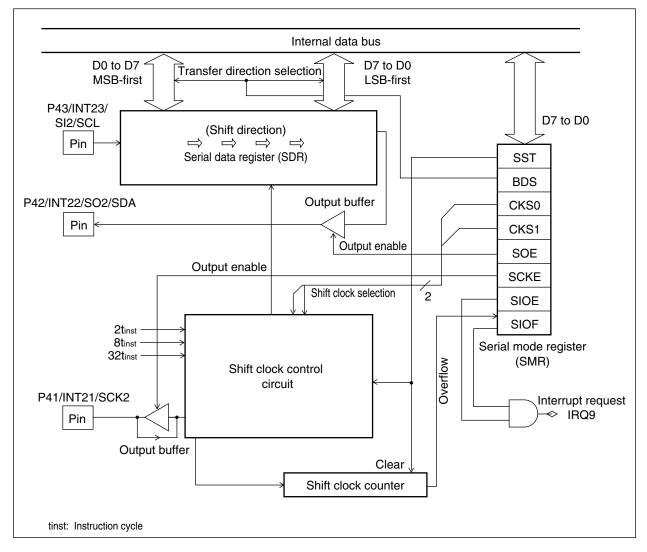

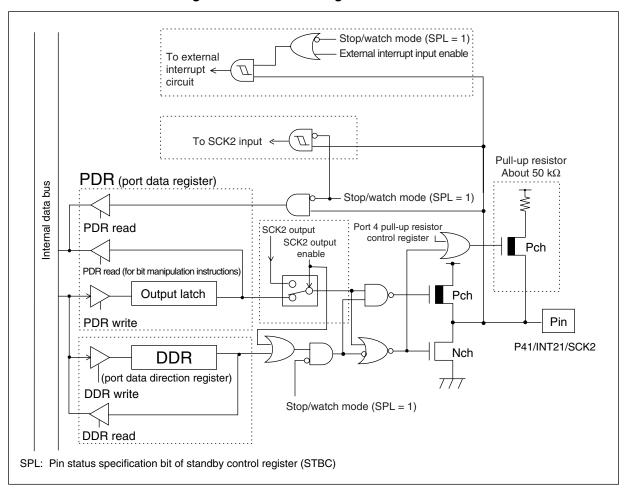

### CHAPTER 18 "8-BIT SERIAL I/O"

This chapter describes the functions and operations of the 8-bit serial I/O.

### CHAPTER 19 "I<sup>2</sup>C INTERFACE"

This chapter describes the functions and operations of the I<sup>2</sup>C bus Interface.

### CHAPTER 20 "WILD REGISTER FUNCTION"

This chapter describes the functions and operations of the wild register function.

### CHAPTER 21 "CLOCK OUTPUT"

This chapter describes the functions and operations of the clock output function.

### CHAPTER 22 "FLASH MEMORY"

This chapter describes the functions and operations of the flash memory.

### CHAPTER 23 "MB89F538/F538L SERIAL PROGRAMMING"

This chapter describes an example of serial writing connection.

### APPENDIX

This appendix lists the I/O map and instructions.

- Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage

or loss from such failures by incorporating safety design measures into your facility and equipment such

as redundancy, fire protection, and prevention of over-current levels and other abnormal operating

conditions.

- If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

<sup>•</sup> The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

<sup>•</sup> The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

<sup>•</sup> The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

## HOW TO USE THIS MANUAL

### Page Configuration of This Manual

Each section of this manual has a summary below the title. This is to enable the reader to acquire an understanding of the outline of the product.

The titles of the sections are also described in the subsections. This is to let the reader know what section of the manual he or she is consulting.

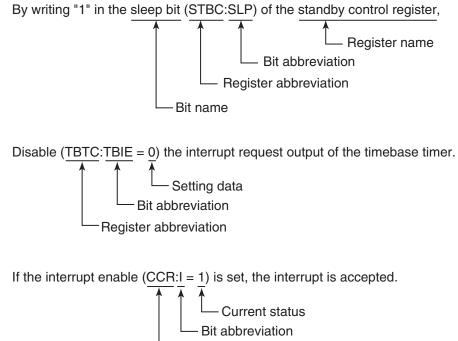

### Example of Notations for the Register and Bit Names

### O Example of the notations for the register and bit names

- Register abbreviation

### **O** Example of the notation for the convertible pin

### P34/PT02 pin

A convertible pin is available which can be used by switching its functions by program settings. The convertible pin is represented by separating the name of each function by "/".

# CONTENTS

| CHAPT          | ER 1 OVERVIEW                                                                  | 1  |

|----------------|--------------------------------------------------------------------------------|----|

| 1.1            | Features of the MB89530/530H/530A Series                                       | 2  |

| 1.2            | Available Models of the MB89530/530H/530A Series                               | 5  |

| 1.3            | Differences among Models and the Precautions to Be Taken When Selecting Models | 8  |

| 1.4            | Block Diagram of the MB89530/530H/530A Series                                  | 10 |

| 1.5            | Pin Layout                                                                     | 11 |

| 1.6            | External Dimension Diagram                                                     | 14 |

| 1.7            | Explanations of the Pin Functions                                              | 21 |

| 1.8            | I/O Circuit Format                                                             | 26 |

| CHAPT          | ER 2 HANDLING DEVICE                                                           | 29 |

| 2.1            | Notes on Handling Devices                                                      | 30 |

| CHAPT          | ER 3 CPU                                                                       | 33 |

| 3.1            | Memory Space                                                                   | 34 |

| 3.1.1          | Special Areas                                                                  | 36 |

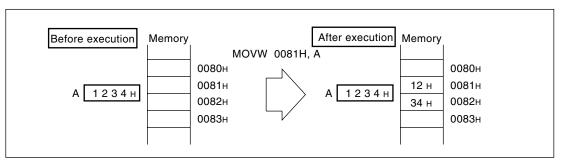

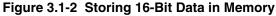

| 3.1.2          | Storing 16-bit Data in Memory                                                  | 38 |

| 3.2            | Dedicated Registers                                                            |    |

| 3.2.1          | Condition Code Register (CCR)                                                  | 41 |

| 3.2.2          | Register Bank Pointer (RP)                                                     | 44 |

|                | General-purpose Registers                                                      |    |

| 3.4            | Interrupts                                                                     |    |

| 3.4.1          | ······································                                         |    |

| 3.4.2          | 1 5                                                                            |    |

| 3.4.3          |                                                                                |    |

| 3.4.4          |                                                                                |    |

| 3.4.5          |                                                                                |    |

| 3.4.6          | 1 5                                                                            |    |

|                | Resets                                                                         |    |

| 3.5.1          |                                                                                |    |

| 3.5.2          | •                                                                              |    |

| 3.5.3          | 3                                                                              |    |

|                |                                                                                |    |

| 3.6.1          |                                                                                |    |

| 3.6.2          |                                                                                |    |

| 3.6.3          | <b>,</b>                                                                       |    |

| 3.6.4          |                                                                                |    |

| 3.6.5          |                                                                                |    |

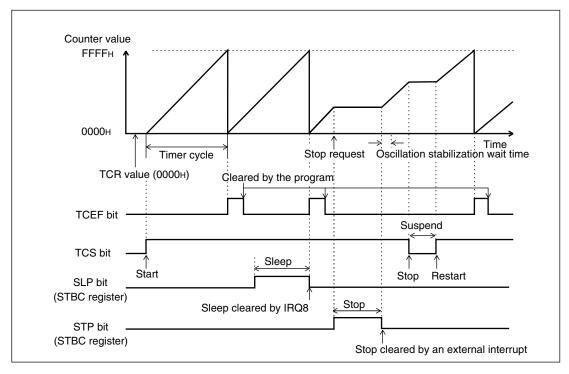

|                | Standby Mode (Low Power Consumption)                                           |    |

| 3.7.1          | Operating State in Standby Mode                                                |    |

| 3.7.2          | •                                                                              |    |

| 3.7.3<br>3.7.4 | •                                                                              |    |

| 3.7.4          |                                                                                |    |

| 0.7.0          |                                                                                |    |

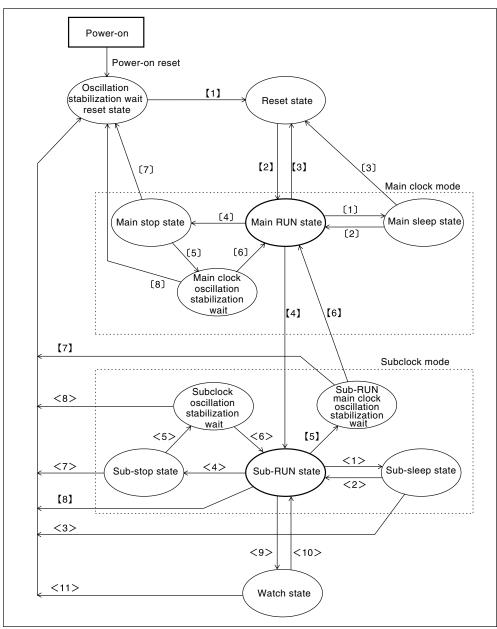

| 3.7  | 7.6 State Transition Diagram 1 (Power-On Reset and Dual Clock System)     | 85  |

|------|---------------------------------------------------------------------------|-----|

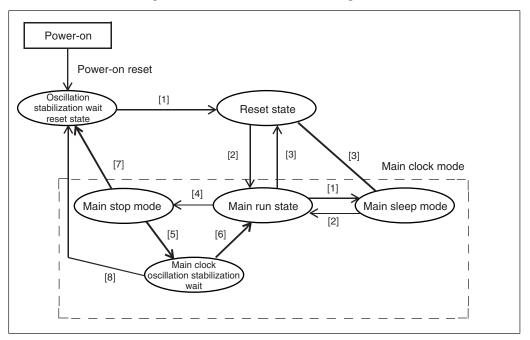

| 3.7  | 7.7 State Transition Diagram 2 (Single Clock System Option)               | 88  |

| 3.7  | 7.8 Notes on Using Standby Mode                                           | 90  |

| 3.8  | Memory Access Mode                                                        | 92  |

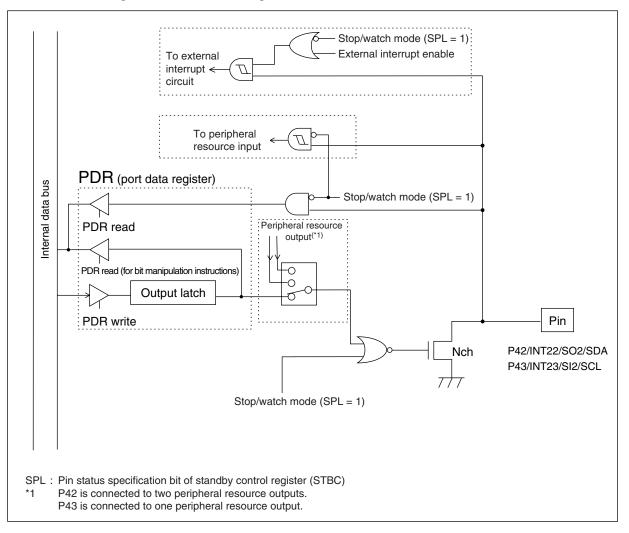

| СНАР | PTER 4 I/O PORTS                                                          | 95  |

| 4.1  | Overview of the I/O Ports                                                 | 96  |

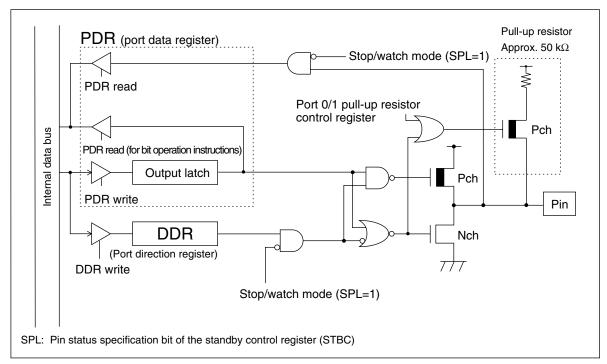

| 4.2  | Port 0 and Port 1                                                         | 99  |

| 4.2  | 2.1 Registers of Port 0 and Port 1 (PDR0, DDR0, PURR0, PDR1, DDR1, PURR1) | 101 |

| 4.2  | 2.2 Operation of Port 0 and Port 1                                        |     |

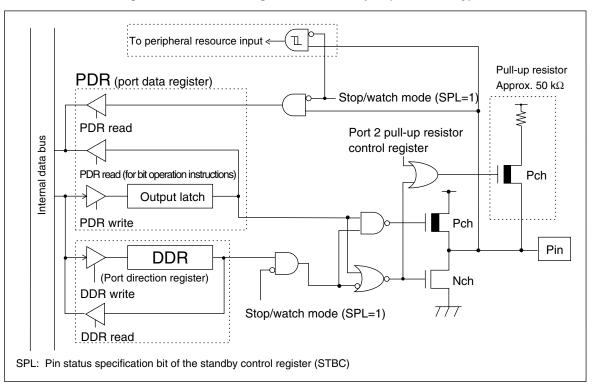

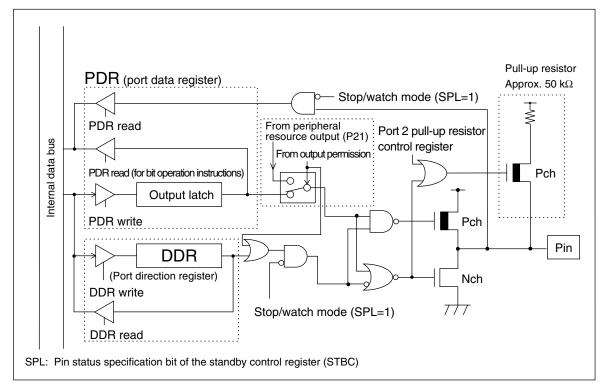

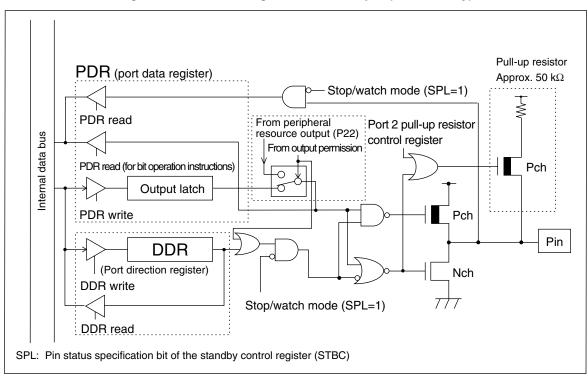

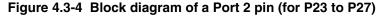

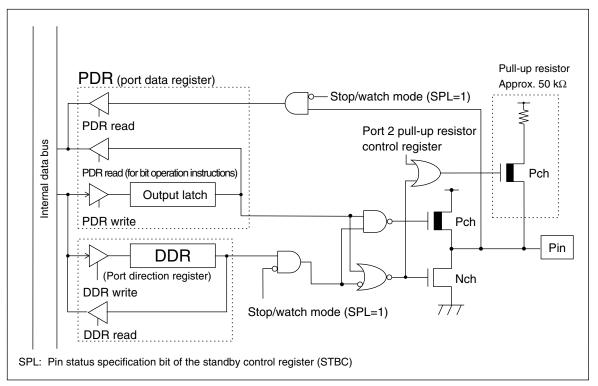

| 4.3  | •                                                                         |     |

| 4.3  |                                                                           |     |

| 4.3  | 3.2 Operation of Port 2                                                   |     |

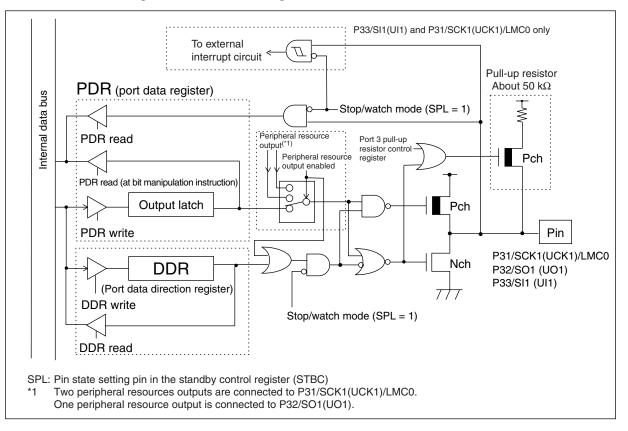

| 4.4  | Port 3                                                                    |     |

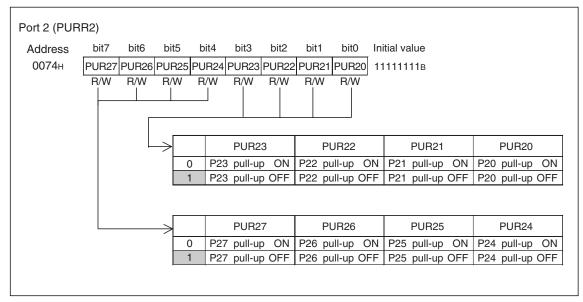

| 4.4  |                                                                           |     |

| 4.4  | 4.2 Operation of Port 3                                                   |     |

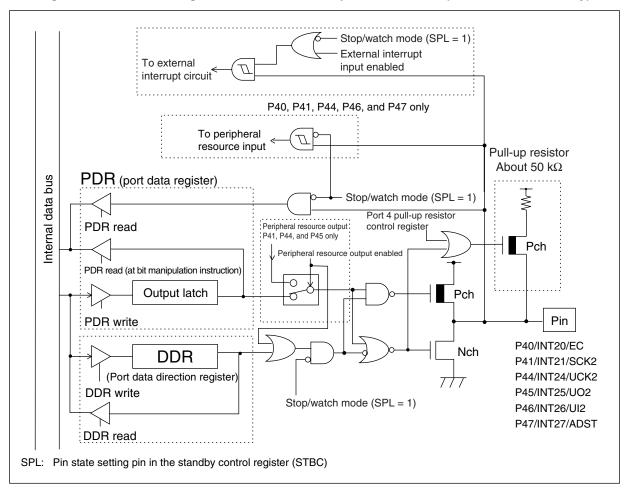

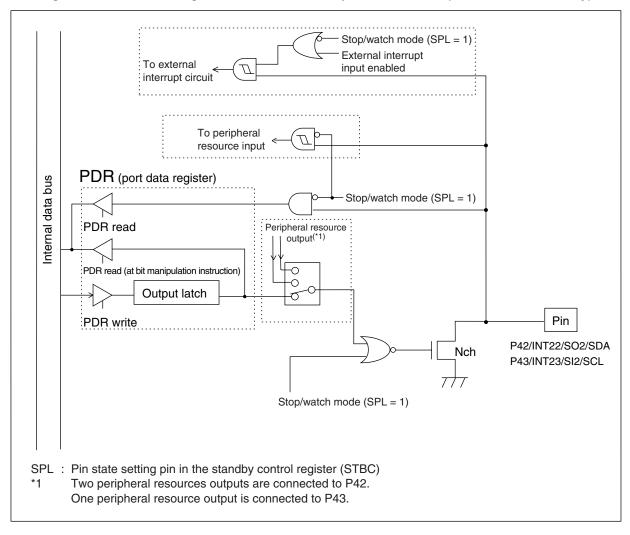

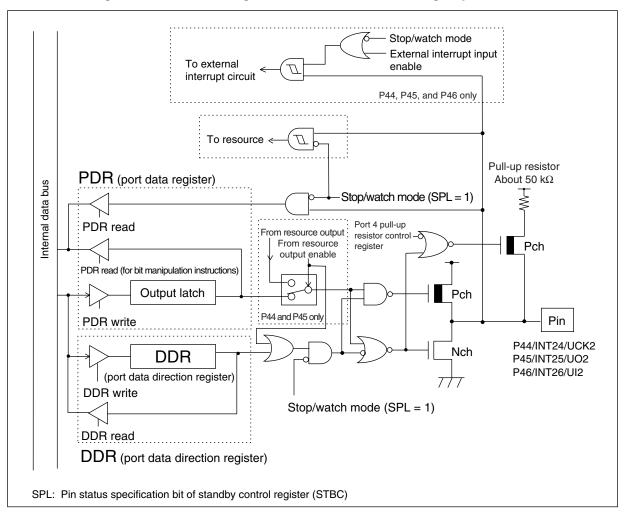

| 4.5  | ·                                                                         |     |

| 4.5  |                                                                           |     |

|      | 5.2 Operation of Port 4                                                   |     |

| 4.6  | •                                                                         |     |

| 4.6  |                                                                           |     |

|      | 6.2 Operation of Port 5                                                   |     |

| 4.7  | ·                                                                         |     |

| 4.7  |                                                                           |     |

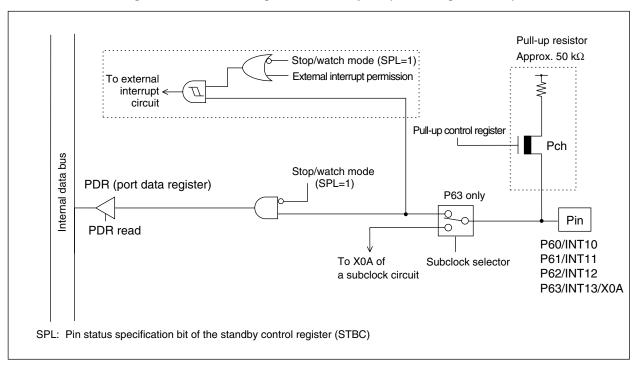

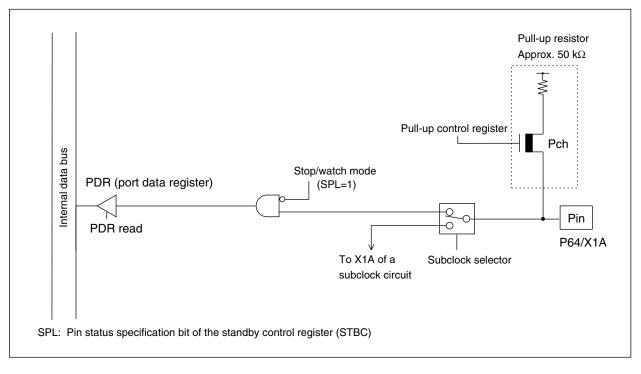

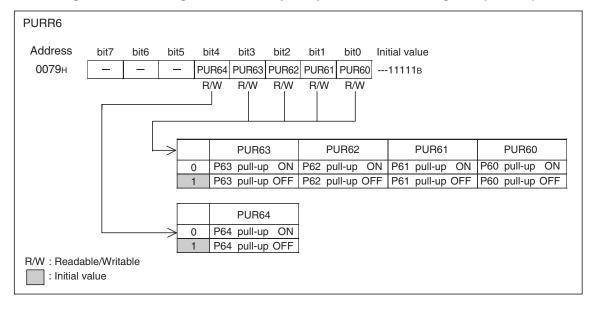

|      | 7.2 Operation of Port 6                                                   |     |

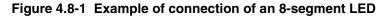

| 4.8  | Sample I/O Port Program                                                   |     |

| СНАР | PTER 5 TIMEBASE TIMER                                                     | 143 |

| 5.1  | Overview of the Timebase Timer                                            | 144 |

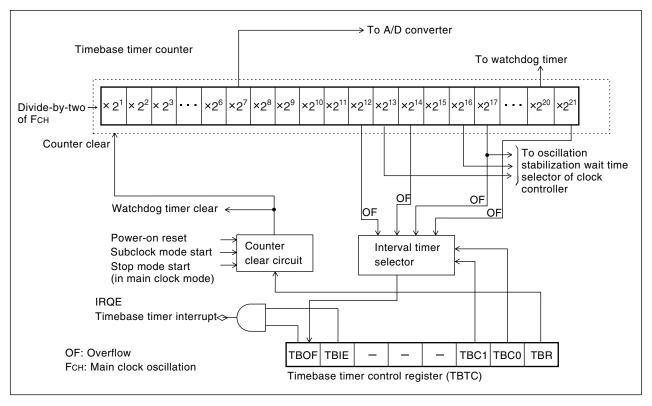

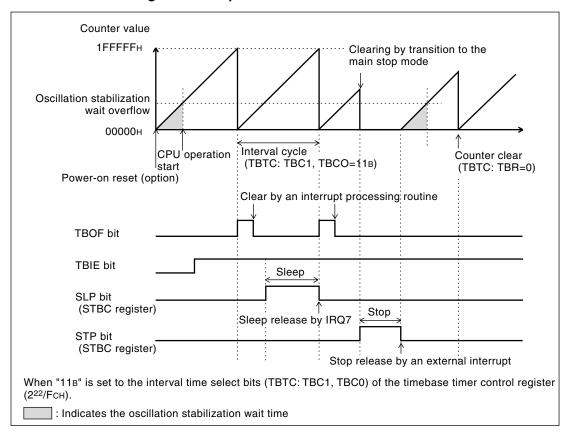

| 5.2  | Configuration of the Timebase Timer                                       |     |

| 5.3  | Timebase Timer Control Register (TBTC)                                    |     |

| 5.4  | Timebase Timer Interrupt                                                  |     |

| 5.5  | Operation of the Timebase Timer                                           |     |

| 5.6  | Notes on Using the Timebase Timer                                         |     |

| 5.7  | Program Example of the Timebase Timer                                     |     |

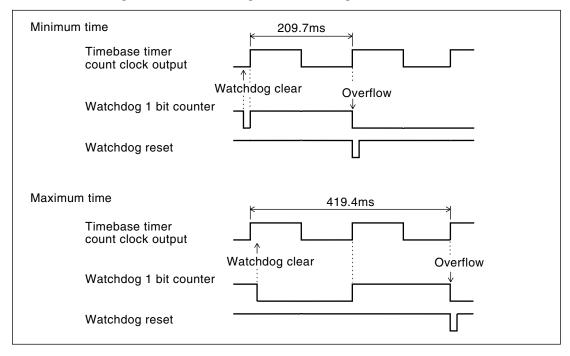

| СНАР | PTER 6 WATCHDOG TIMER                                                     | 155 |

| 6.1  | Overview of the Watchdog Timer                                            | 156 |

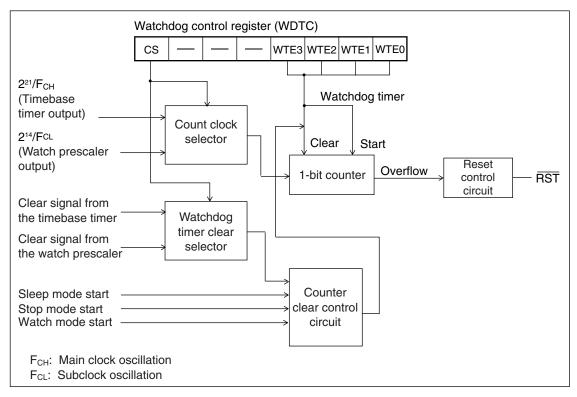

| 6.2  | Configuration of the Watchdog Timer                                       |     |

| 6.3  | Watchdog Timer Control Register (WDTC)                                    |     |

| 6.4  | Operation of the Watchdog Timer                                           |     |

| 6.5  | Notes on Using the Watchdog Timer                                         |     |

| 6.6  | Program Example of the Watchdog Timer                                     |     |

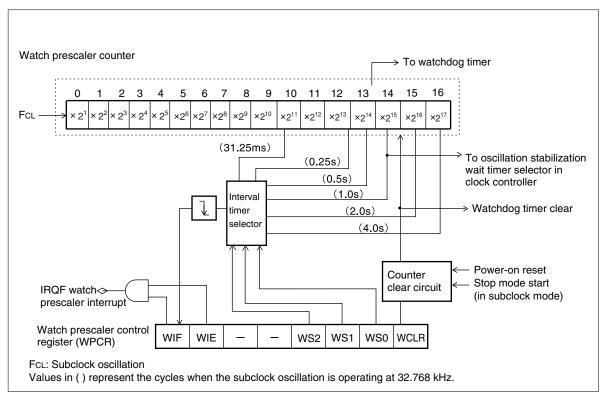

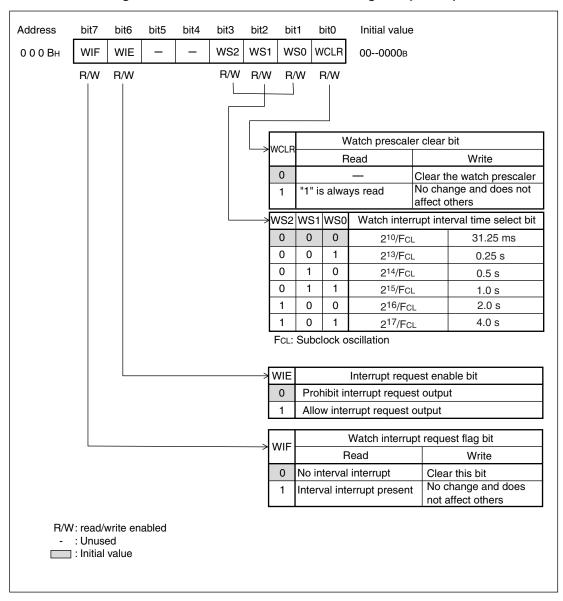

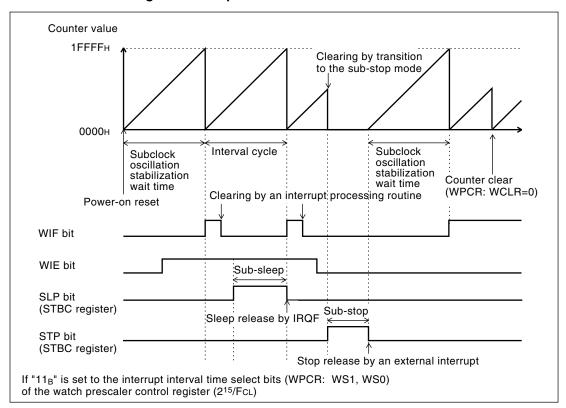

| СНАР | PTER 7 WATCH PRESCALER                                                    | 167 |

| 7.1  | Overview of the Watch Prescaler                                           | 168 |

| 7.2  | Configuration of the Watch Prescaler                                      |     |

| 7.3  | Watch Prescaler Control Register (WPCR)                                   |     |

|      |                                                                           |     |

| 7  | 7.4  | Watch Prescaler Interrupt                                                               | 174   |

|----|------|-----------------------------------------------------------------------------------------|-------|

| 7  | 7.5  | Operation of the Watch Prescaler                                                        | 175   |

| 7  | 7.6  | Notes on Using the Watch Prescaler                                                      | 177   |

| 7  | 7.7  | Program Example of the Watch Prescaler                                                  | 178   |

| СН | AP1  | FER 8       2-CHANNEL 8-BIT PWM TIMERS                                                  | 179   |

| 8  | 3.1  | Overview of the 2-Channel 8-Bit PWM Timer (Interval Timer Function)                     | 180   |

| 8  | 3.2  | Overview of the 2-Channel 8-Bit PWM Timer (PWM Timer Function)                          | 183   |

| 8  | 3.3  | Configuration of the 2-Channel 8-Bit PWM Timer                                          | 186   |

| 8  | 3.4  | Pins of the 2-Channel 8-Bit PWM Timer                                                   | 188   |

| 8  | 3.5  | Registers of the 2-Channel 8-Bit PWM Timer                                              | 190   |

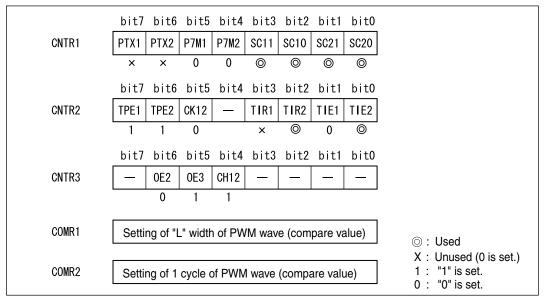

|    | 8.5. | 1 PWM Control Register 1 (CNTR1)                                                        | 191   |

|    | 8.5. | 5 ( )                                                                                   |       |

|    | 8.5. | 3 PWM Control Register 3 (CNTR3)                                                        | 195   |

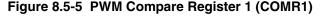

|    | 8.5. | 4 PWM Compare Register 1 (COMR1)                                                        | 197   |

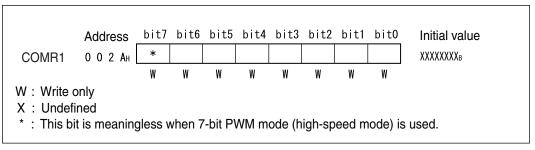

|    | 8.5. | 5 PWM Compare Register 2 (COMR2)                                                        | 199   |

| 8  | 3.6  | 2-Channel 8-Bit PWM Timer Interrupts                                                    | 201   |

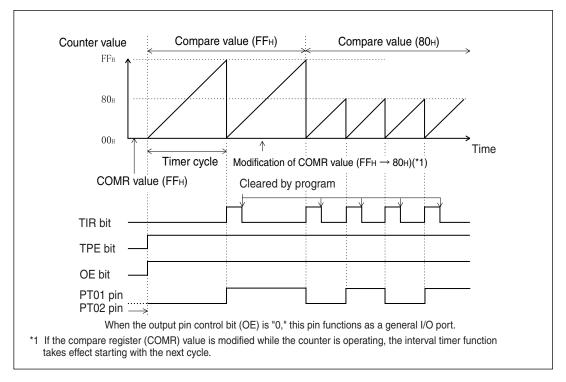

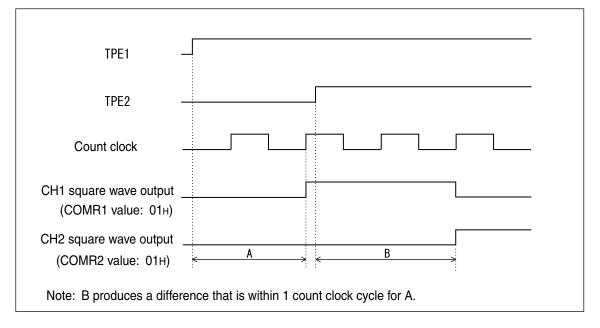

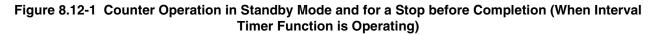

| 8  | 3.7  | Interval Timer Function Operation                                                       |       |

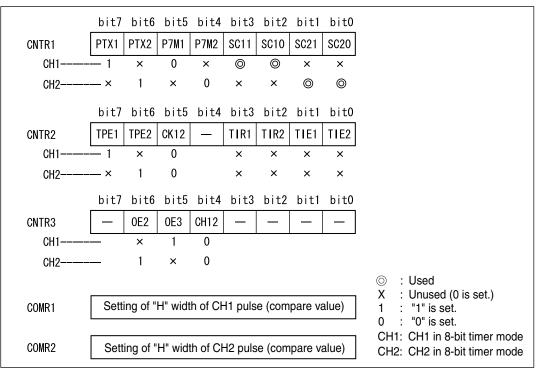

| 8  | 8.8  | Explanation of the 2-Channel 8-Bit PWM Timer Operation in 8-Bit PWM Mode                |       |

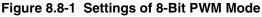

| 8  | 3.9  | 2-Channel 8-Bit PWM Timer Operation in 7-Bit PWM Mode                                   |       |

| 8  | 3.10 | Explanation of the 2-Channel 8-Bit PWM Timer Operation in CH12PWM Mode                  |       |

| 8  | 3.11 | Explanation of the Prescaler Operation of 2-Channel 8-Bit PWM Timer                     |       |

| 8  | 3.12 | State of the 2-Channel 8-Bit PWM Timer Operation in Each Mode                           |       |

| -  | 3.13 | Notes on Using the 2-Channel 8-Bit PWM Timer Usage                                      |       |

|    | 3.14 | Program Examples of the 2-Channel 8-Bit PWM Timer (Interval Timer Function)             |       |

| 8  | 3.15 | Program Examples of the 2-Channel 8-Bit PWM Timer (PWM Timer Function)                  | 220   |

| СН | AP1  | FER 9 PULSE WIDTH COUNT TIMER (PWC)                                                     | 223   |

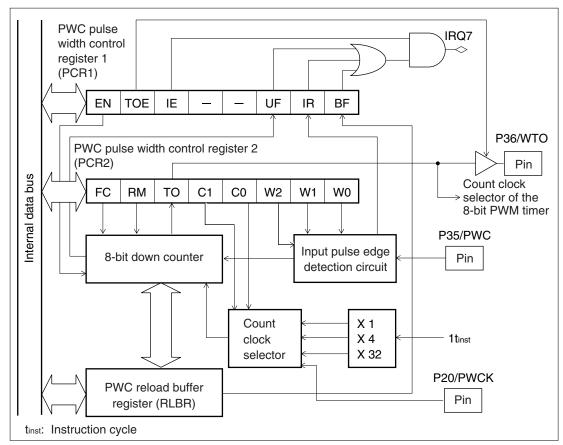

| ę  | 9.1  | Overview of the Pulse Width Count Timer                                                 | 224   |

| g  | 9.2  | Configuration of the Pulse Width Count Timer                                            | 226   |

| g  | 9.3  | Pins of the Pulse Width Count Timer                                                     | 228   |

| g  | 9.4  | Registers of the Pulse Width Count Timer                                                | 231   |

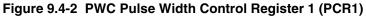

|    | 9.4. | 1 PWC Pulse Width Control Register 1 (PCR1)                                             | 232   |

|    | 9.4. | 2 PWC Pulse Width Control Register 2 (PCR2)                                             | 235   |

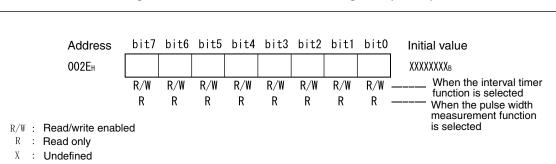

|    | 9.4. | 3 PWC Reload Buffer Register (RLBR)                                                     | 237   |

| ę  | 9.5  | Pulse Width Count Timer Interrupts                                                      | 239   |

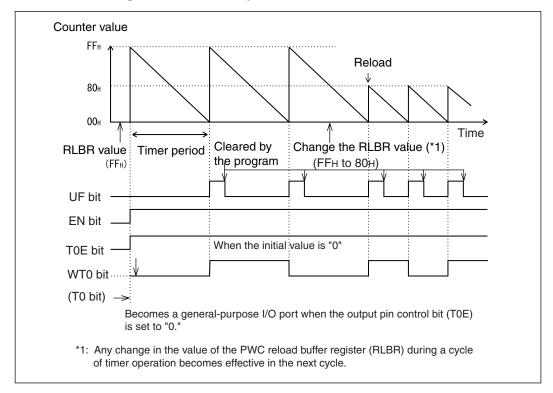

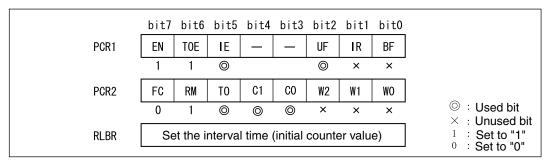

| g  | 9.6  | Operation of the Interval Timer Function                                                | 241   |

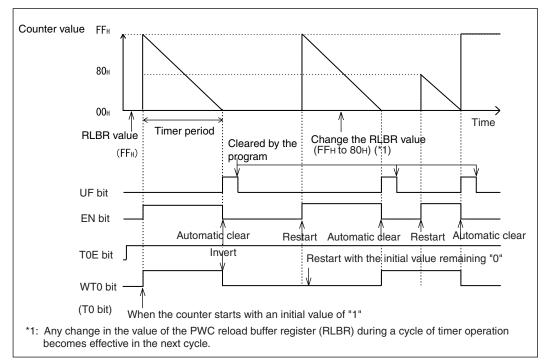

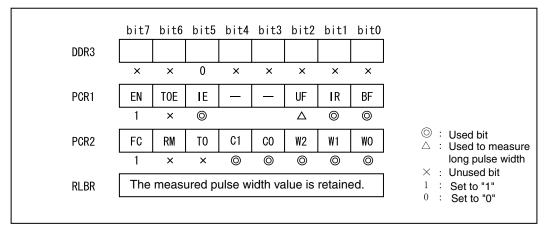

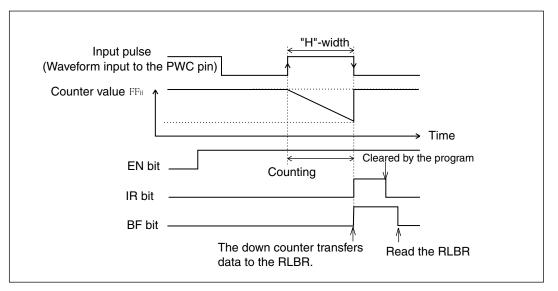

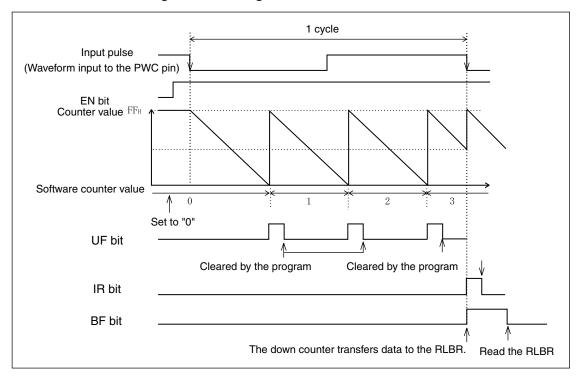

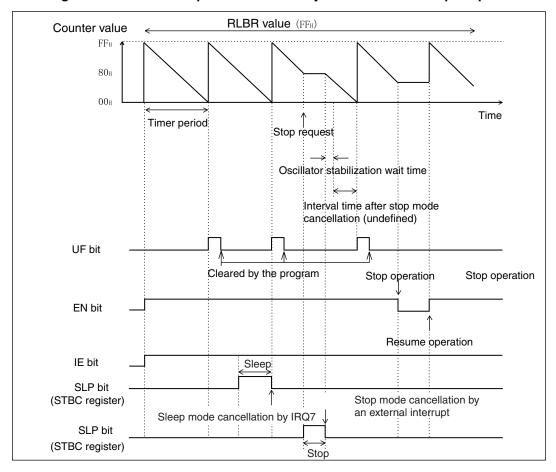

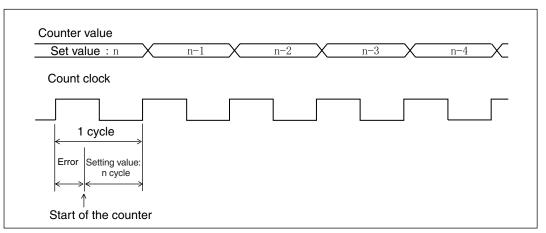

| ę  | 9.7  | Operation of the Pulse Width Measurement Function                                       |       |

| ę  | 9.8  | Status of the Pulse Width Count Timer in Each Mode                                      | 247   |

| ę  | 9.9  | Notes on Using the Pulse Width Count Timer                                              |       |

| ę  | 9.10 | Program Examples for the Interval Timer Function of the Pulse Width Count Timer         |       |

| ç  | 9.11 | Program Example for the Pulse Width Measurement Function of the Pulse Width Count Timer | 253   |

| СН | AP1  | TER 10 6-BIT PPG TIMER                                                                  | . 255 |

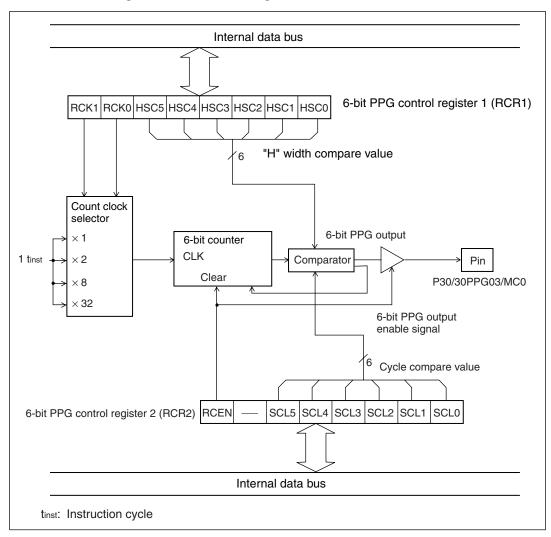

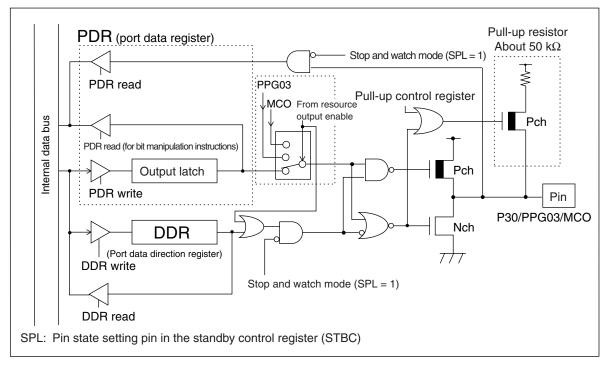

| 1  | 0.1  | Overview of the 6-Bit PPG Timer                                                         | 256   |

| 1  | 0.2  | Configuration of the 6-Bit PPG Timer Circuit                                            |       |

|    |      | Pins of the 6-Bit PPG Timer                                                             |       |

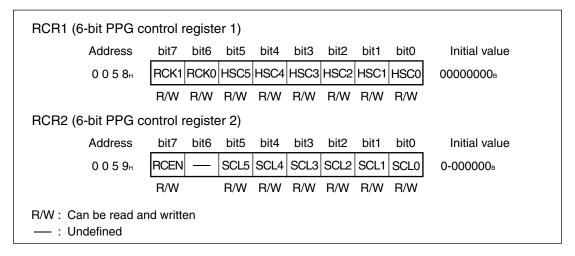

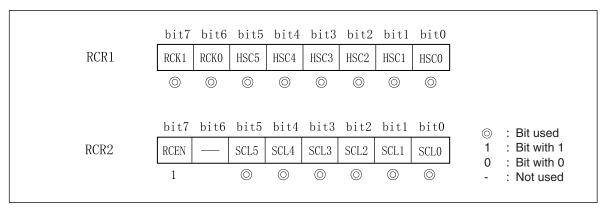

| 10.4.1 6-Bit PPG Control Register 1 (RCR1)                | 263 |

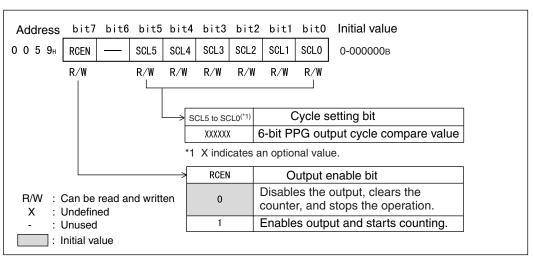

|-----------------------------------------------------------|-----|

| 10.4.2 6-Bit PPG Control Register 2 (RCR2)                |     |

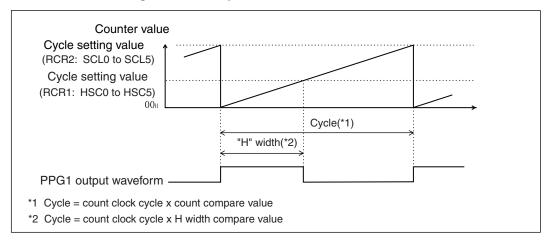

| 10.5 Operation of the 6-Bit PPG Timer                     |     |

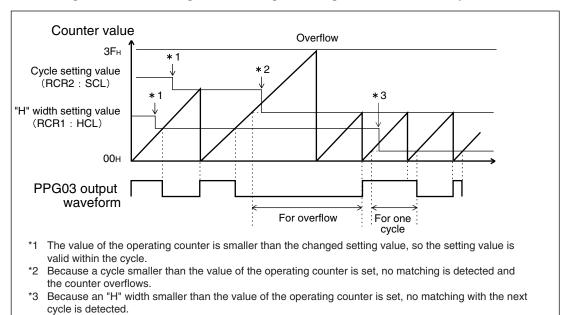

| 10.6 Notes on Using the 6-Bit PPG Timer                   |     |

| 10.7 Program Example of the 6-Bit PPG Timer Programs      |     |

|                                                           |     |

| CHAPTER 11 12-BIT PPG TIMER                               |     |

| 11.1 Overview of the 12-Bit PPG Timer                     |     |

| 11.2 Configuration of the 12-Bit PPG Timer Circuit        |     |

| 11.3 Pins of the 12-Bit PPG Timer                         |     |

| 11.4 Registers of the 12-Bit PPG Timer                    |     |

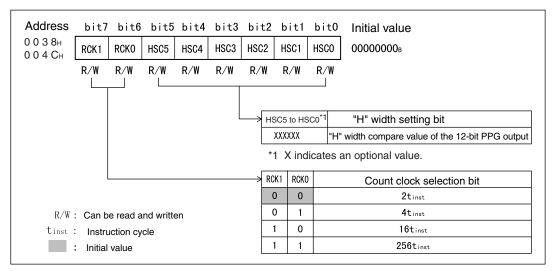

| 11.4.1 12-Bit PPG Control Register 1 (PPGC1/PPGC2)        | 278 |

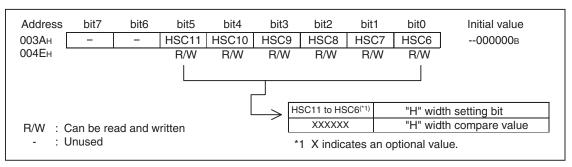

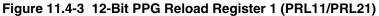

| 11.4.2 12-Bit PPG Reload Register 1 (PRL11/PRL21)         | 279 |

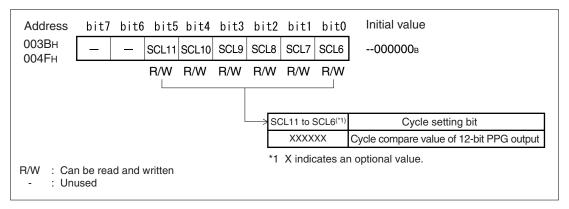

| 11.4.3 12-Bit PPG Reload Register 2 (PRL12/PRL22)         | 280 |

| 11.4.4 12-Bit PPG Reload Register 3 (PRL13/PRL23)         | 281 |

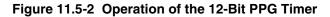

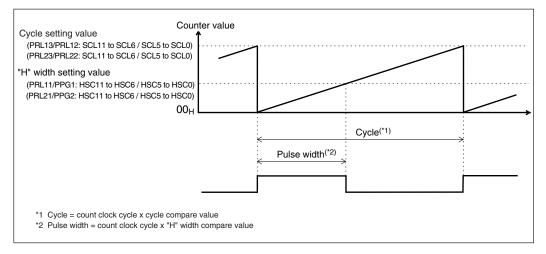

| 11.5 Operation of the 12-Bit PPG Timer                    | 282 |

| 11.6 Notes on Using the 12-Bit PPG Timer                  | 283 |

| 11.7 Program Example of the 12-Bit PPG Timer              | 285 |

|                                                           | 007 |

| CHAPTER 12 16-BIT TIMER/COUNTER                           |     |

| 12.1 Overview of the 16-bit Timer/Counter                 |     |

| 12.2 Configuration of the 16-bit Timer/Counter            |     |

| 12.3 Pin of the 16-bit Timer/Counter                      |     |

| 12.4 Registers of the 16-bit Timer/Counter                |     |

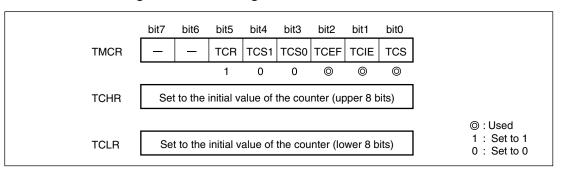

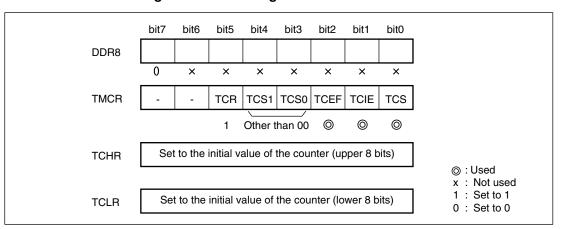

| 12.4.1 Timer Control Register (TMCR)                      |     |

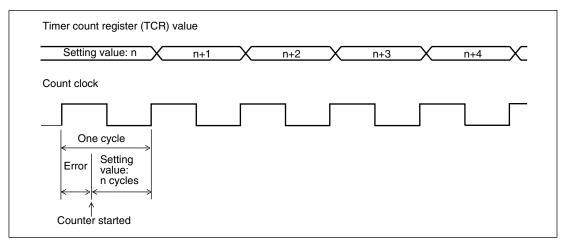

| 12.4.2 16-bit Timer Count Register (TCR)                  |     |

| 12.5 16-bit Timer/Counter Interrupts                      |     |

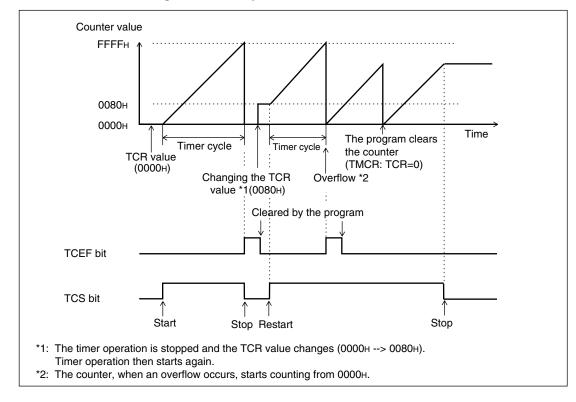

| 12.6 Operation of the Interval Timer Function             |     |

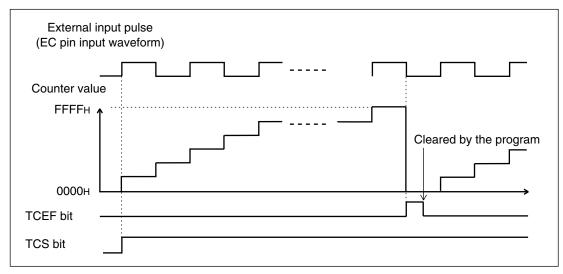

| 12.7 Operation of the Counter Function                    |     |

| 12.8 Status of the 16-bit Timer/Counter in Each Mode      |     |

| 12.9 Notes on Using the 16-bit Timer/Counter              |     |

| 12.10 Programe Example of the 16-bit Timer/Counter        | 304 |

| CHAPTER 13 EXTERNAL INTERRUPT CIRCUIT 1 (EDGE)            | 309 |

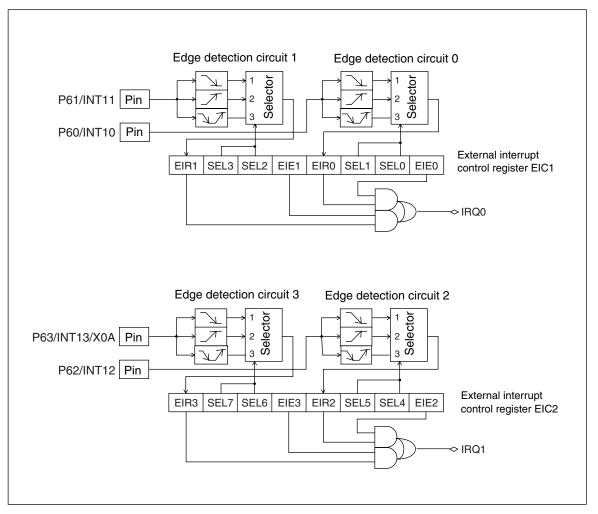

| 13.1 Overview of External Interrupt Circuit 1             |     |

| 13.2 Configuration of the External Interrupt Circuit 1    | 311 |

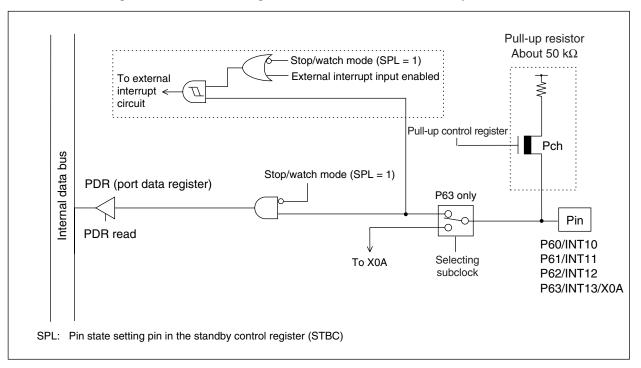

| 13.3 Pins of the External Interrupt Circuit 1             | 313 |

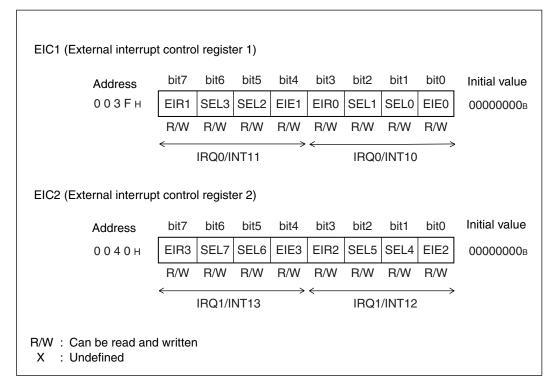

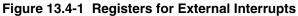

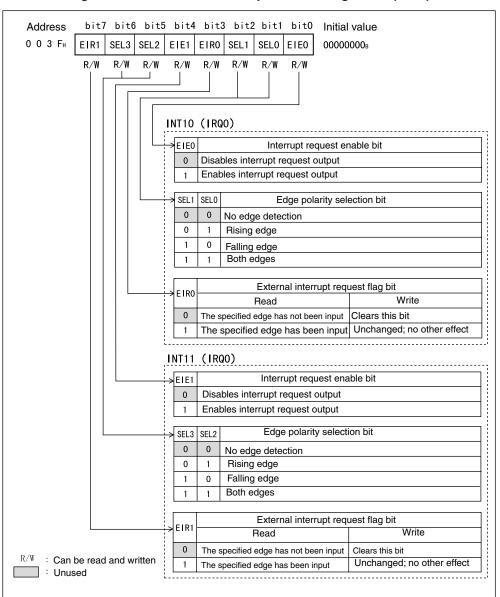

| 13.4 Registers of the External Interrupt Circuit 1        | 315 |

| 13.4.1 External Interrupt Control Register 1 (EIC1)       | 316 |

| 13.4.2 External Interrupt Control Register 2 (EIC2)       |     |

| 13.5 External Interrupt Circuit 1 Interrupts              |     |

| 13.6 Operation of the External Interrupt Circuit 1        |     |

| 13.7 Program Example of the External Interrupt Circuit 1  |     |

|                                                           |     |

| CHAPTER 14 EXTERNAL INTERRUPT CIRCUIT 2 (LEVEL)           |     |

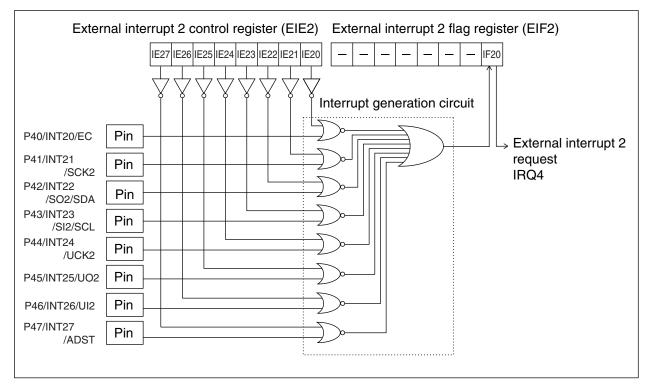

| 14.1 Overview of the External Interrupt Circuit 2 (Level) |     |

| 14.2 Configuration of the External Interrupt Circuit 2    |     |

| 14.3 Pins of the External Interrupt Circuit 2             | 329 |

| 14.4 Registers of the External Interrupt Circuit 2       |  |

|----------------------------------------------------------|--|

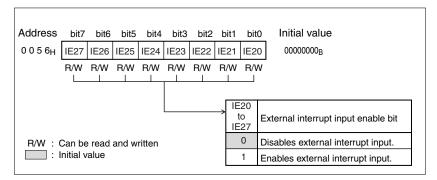

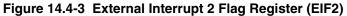

| 14.4.1 External Interrupt 2 Control Register (EIE2)      |  |

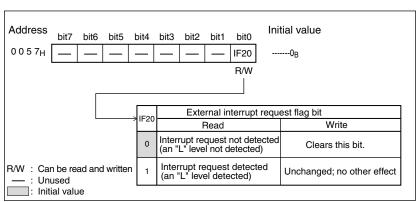

| 14.4.2 External Interrupt 2 Flag Register (EIF2)         |  |

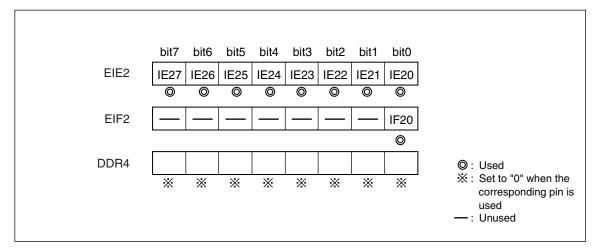

| 14.5 External Interrupt Circuit 2 Interrupts             |  |

| 14.6 Operation of the External Interrupt Circuit 2       |  |

| 14.7 Program Example of the External Interrupt Circuit 2 |  |

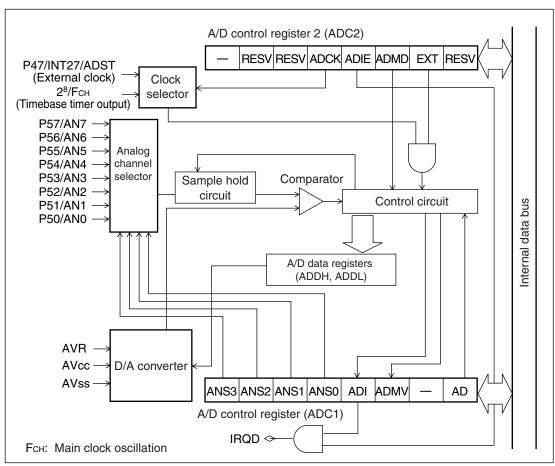

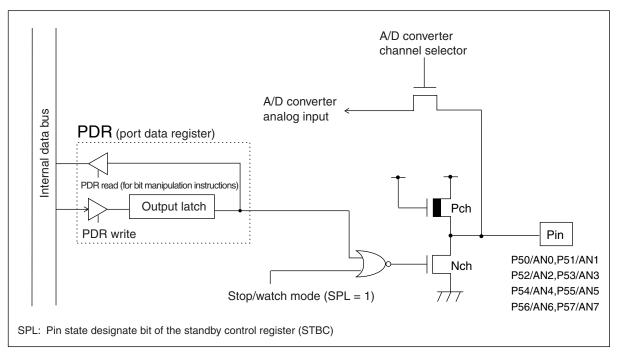

| CHAPTER 15 A/D CONVERTER                                 |  |

| 15.1 Overview of the A/D Converter                       |  |

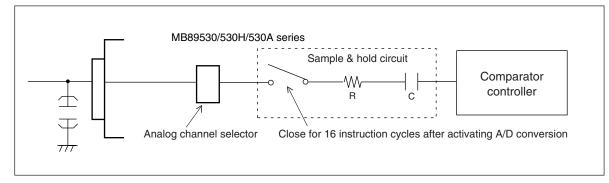

| 15.2 Configuration of the A/D Converter                  |  |

| 15.3 Pins of the A/D Converter                           |  |

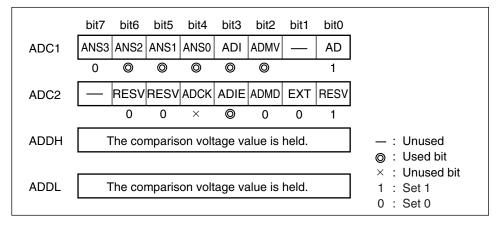

| 15.4 Registers of the A/D Converter                      |  |

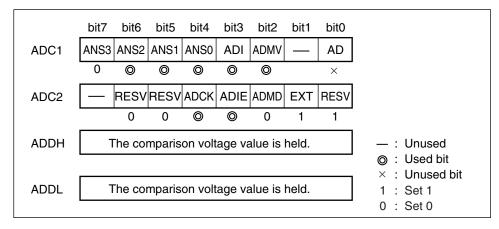

| 15.4.1 A/D Control Register 1 (ADC1)                     |  |

| 15.4.2 A/D Control Register 2 (ADC2)                     |  |

| 15.4.3 A/D Data Registers (ADDH, ADDL)                   |  |

| 15.5 A/D Converter Interrupt                             |  |

| 15.6 Operation of the A/D Converter                      |  |

| 15.7 Notes on Using the A/D Converter                    |  |

| 15.8 Program Example of the A/D Converter                |  |

| CHAPTER 16 UART/SIO                                      |  |

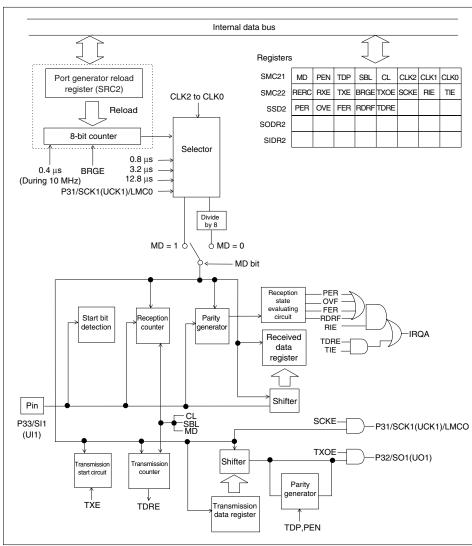

| 16.1 Overview of the UART/SIO                            |  |

| 16.2 Configuration of the UART/SIO                       |  |

| 16.3 Pins of the UART/SIO                                |  |

| 16.4 Registers of the UART/SIO                           |  |

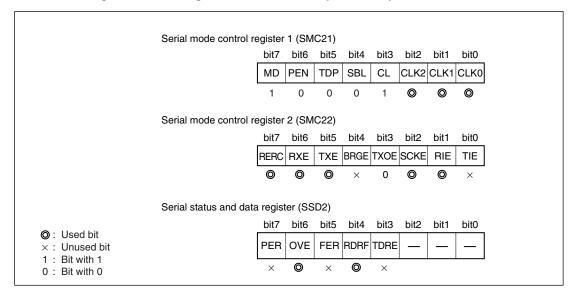

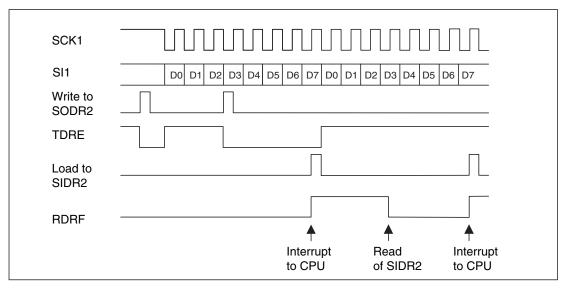

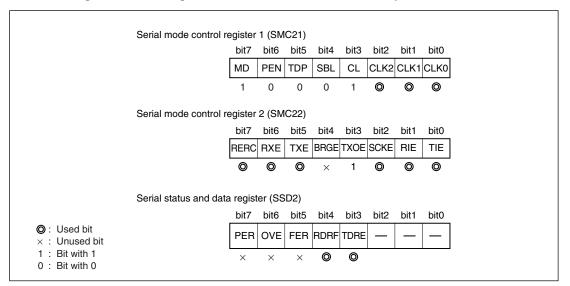

| 16.4.1 Serial Mode Control Register 1 (SMC21)            |  |

| 16.4.2 Serial Mode Control Register 2 (SMC22)            |  |

| 16.4.3 Serial Status/Data Register (SSD2)                |  |

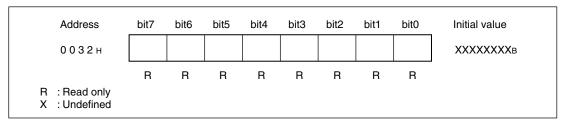

| 16.4.4 Serial Input Data Register (SIDR2)                |  |

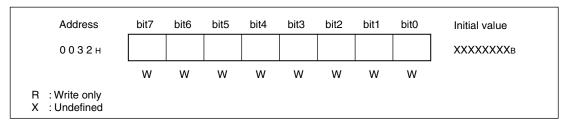

| 16.4.5 Serial Output Data Register (SODR2)               |  |

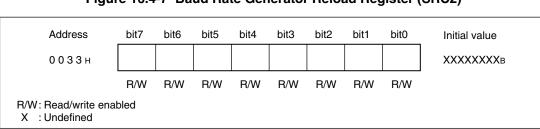

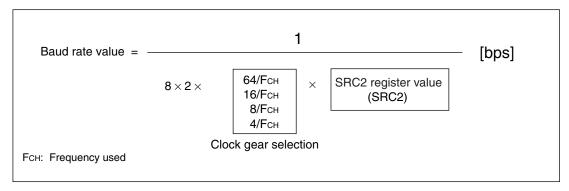

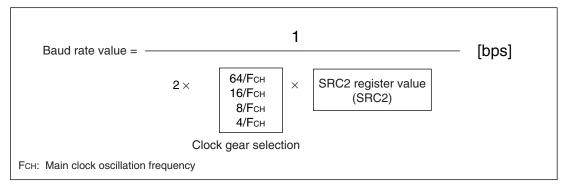

| 16.4.6 Baud Rate Generator Reload Register (SRC2)        |  |

| 16.5 UART/SIO Interrupt                                  |  |

| 16.6 Operation of the UART/SIO                           |  |

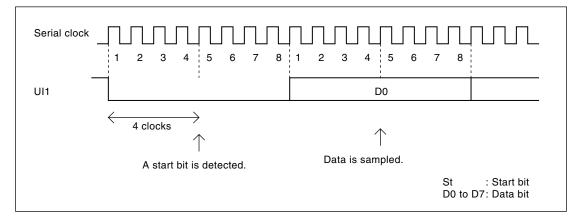

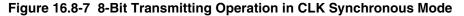

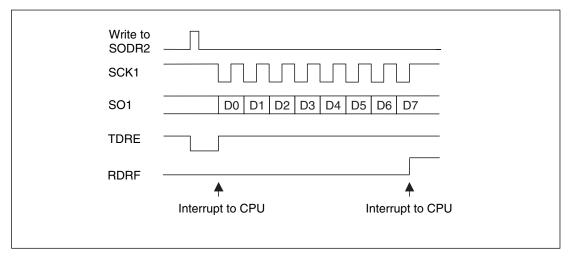

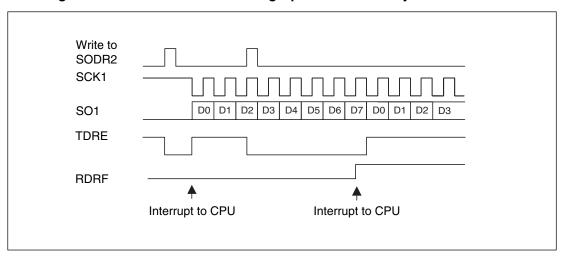

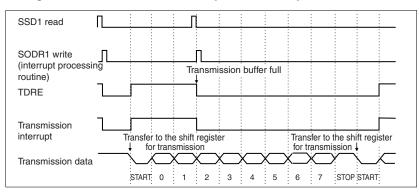

| 16.7 Operation of the Operation Mode 0                   |  |

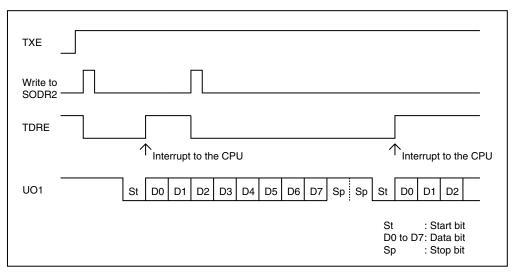

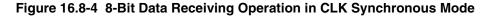

| 16.8 Operation of the Operation Mode 1                   |  |

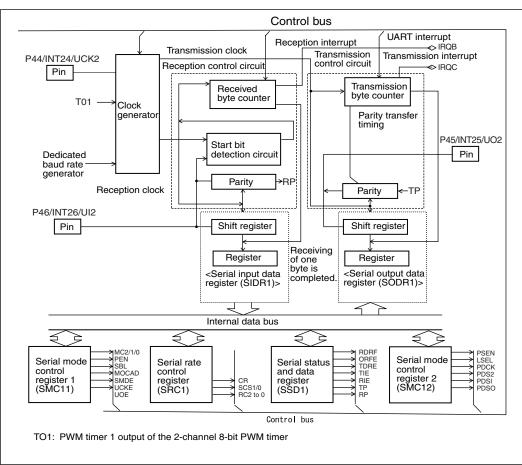

| CHAPTER 17 HIGH-SPEED UART                               |  |

| 17.1 Overview of the High-Speed UART                     |  |

| 17.2 Configuration of the High-Speed UART                |  |

| 17.3 Pins of the High-Speed UART                         |  |

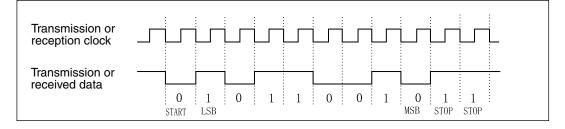

| 17.4 Registers of the High-Speed UART                    |  |

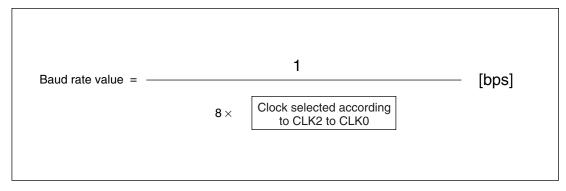

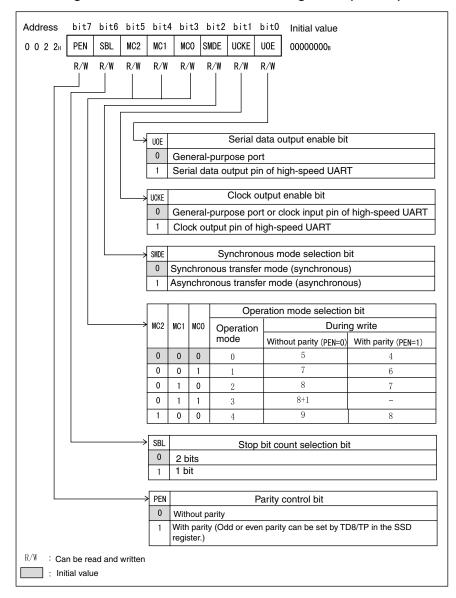

| 17.4.1 Serial Mode Control Register 1 (SMC11)            |  |

| 17.4.2 Serial Mode Control Register 2 (SMC12)            |  |

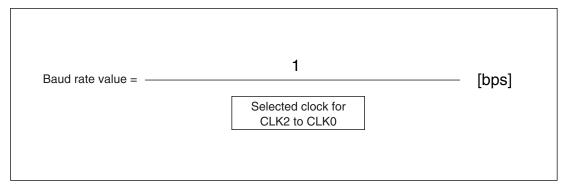

| 17.4.3 Serial Rate Control Register (SRC1)               |  |

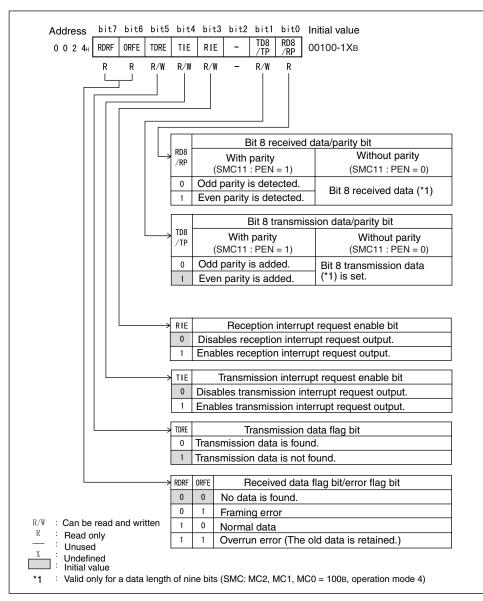

| 17.4.4 Serial Status/Data Register (SSD1)                |  |

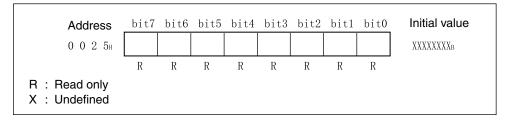

| 17.4.5 Serial Input Data Register (SIDR1)                |  |

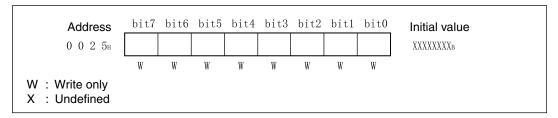

| 17.4.6 Serial Output Data Register (SODR1)               |  |

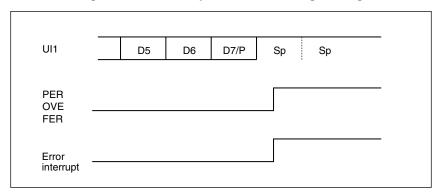

| 17.5 High-Speed UART Interrupts                          |  |

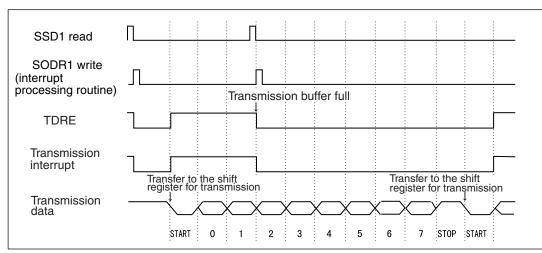

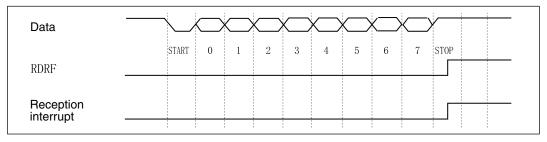

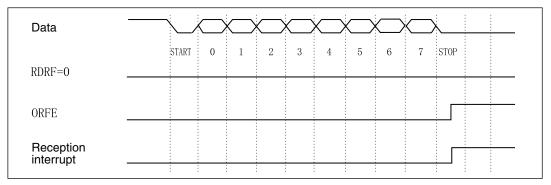

| 17.6 | Operation of the High-Speed UART            | 411 |

|------|---------------------------------------------|-----|

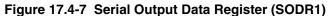

| 17.7 | Operation of Operation Modes 0, 1, 2, and 4 | 412 |

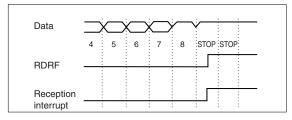

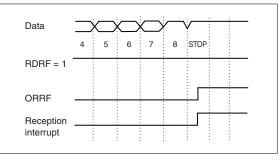

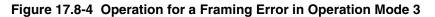

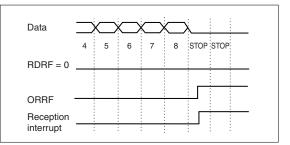

| 17.8 | Operation of Operation Mode 3               | 415 |

| 17.9 | Program Example of the UART                 | 417 |

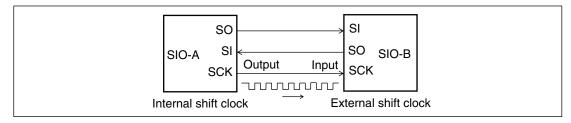

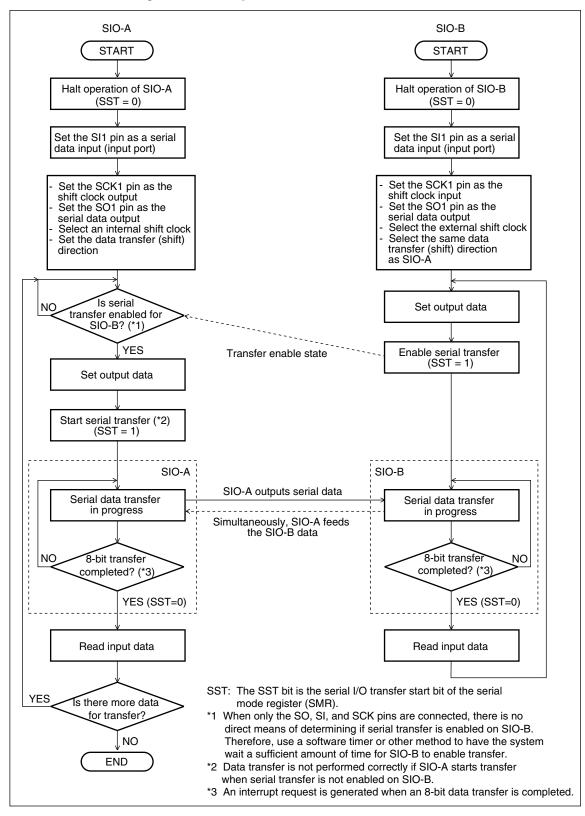

| CHAPTER 18 8-BIT SERIAL I/O                            | 419 |

|--------------------------------------------------------|-----|

| 18.1 Overview of the 8-Bit Serial I/O                  | 420 |

| 18.2 Configuration of the 8-Bit Serial I/O             |     |

| 18.3 Pins of the 8-Bit Serial I/O                      | 423 |

| 18.4 Registers of the 8-Bit Serial I/O                 | 427 |

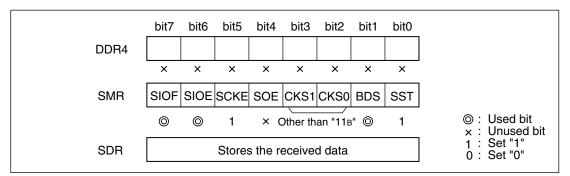

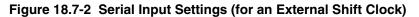

| 18.4.1 Serial Mode Register (SMR)                      |     |

| 18.4.2 Serial Data Register (SDR)                      | 430 |

| 18.5 8-Bit Serial I/O Interrupts                       | 431 |

| 18.6 Operation of the Serial Output                    |     |

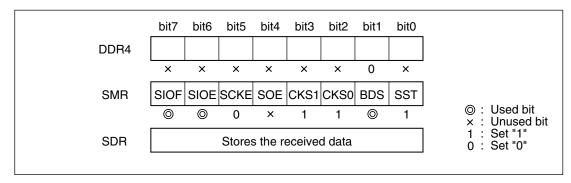

| 18.7 Operation of the Serial Input                     | 434 |

| 18.8 States in Each Mode of 8-Bit Serial I/O Operation | 436 |

| 18.9 Notes on Using the 8-Bit Serial I/O               | 439 |

| 18.10 8-Bit Serial I/O Connection Example              | 440 |

| 18.11 Program Examples of the 8-Bit Serial I/O         | 442 |

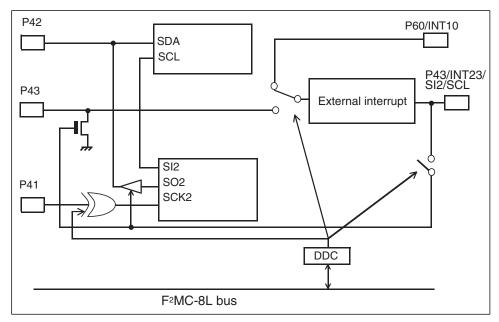

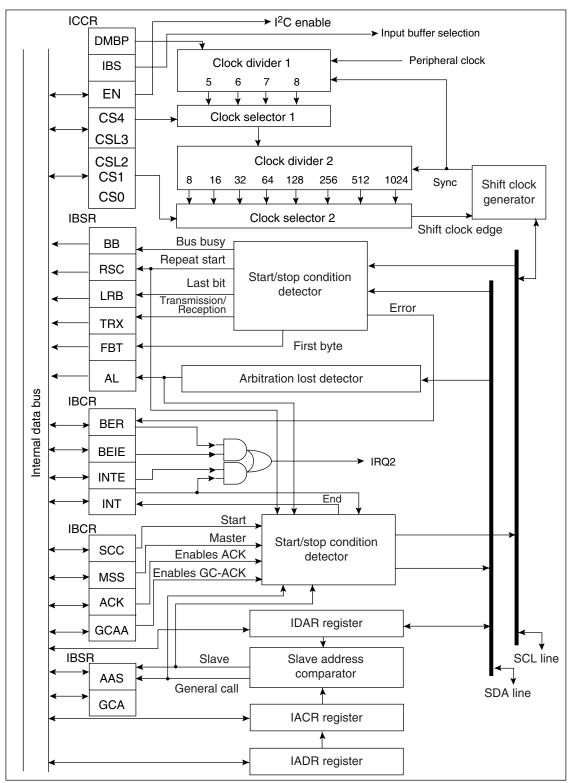

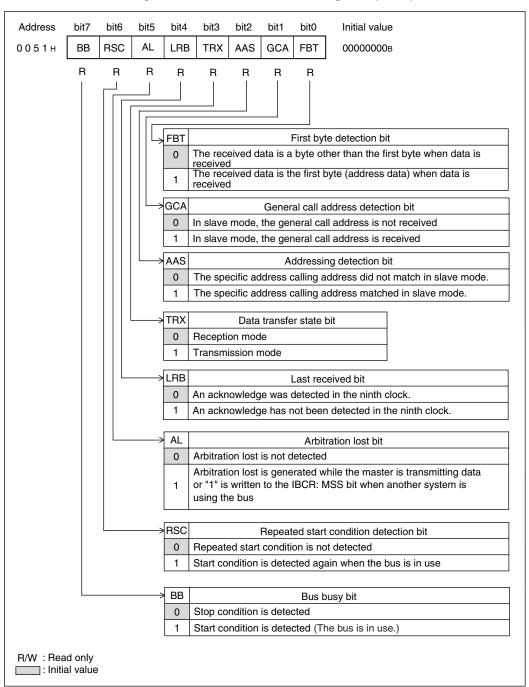

# CHAPTER 19 I<sup>2</sup>C INTERFACE 445 19.1 Overview of the I<sup>2</sup>C Interface 446

| 19.2 Configuration of the I <sup>2</sup> C Interface       | 447 |

|------------------------------------------------------------|-----|

| 19.3 Configuration of the I <sup>2</sup> C Bus Interface   | 451 |

| 19.4 Registers of the I <sup>2</sup> C Bus Interface       | 453 |

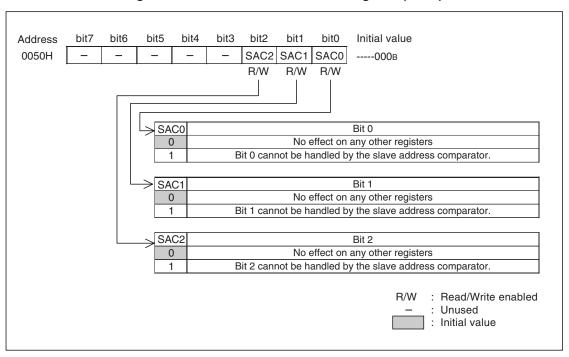

| 19.4.1 I <sup>2</sup> C Address Control Register (IACR)    |     |

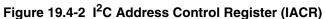

| 19.4.2 I <sup>2</sup> C Bus Status Register (IBSR)         | 456 |

| 19.4.3 I <sup>2</sup> C Bus Control Register (IBCR)        |     |

| 19.4.4 I <sup>2</sup> C Clock Control Register (ICCR)      |     |

| 19.4.5 I <sup>2</sup> C Address Register (IADR)            |     |

| 19.4.6 I <sup>2</sup> C Data Register (IDAR)               | 464 |

| 19.5 I <sup>2</sup> C Interface Interrupts                 | 465 |

| 19.6 Operation of the I <sup>2</sup> C Interface           | 466 |

| 19.7 Notes on Using the I <sup>2</sup> C Bus Interface     | 469 |

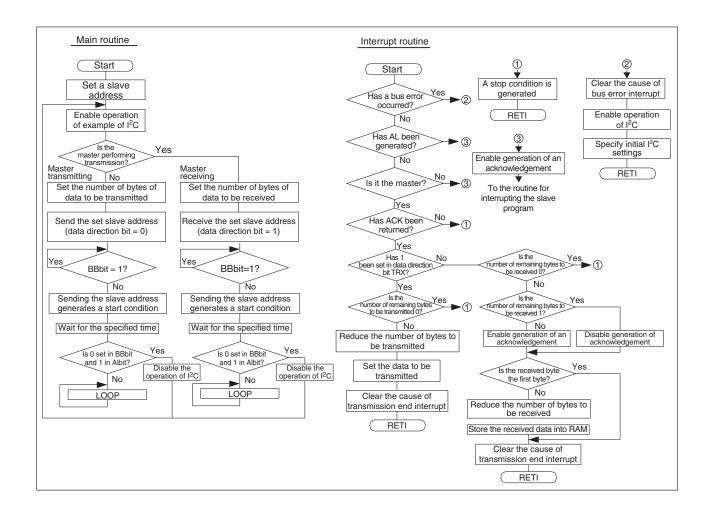

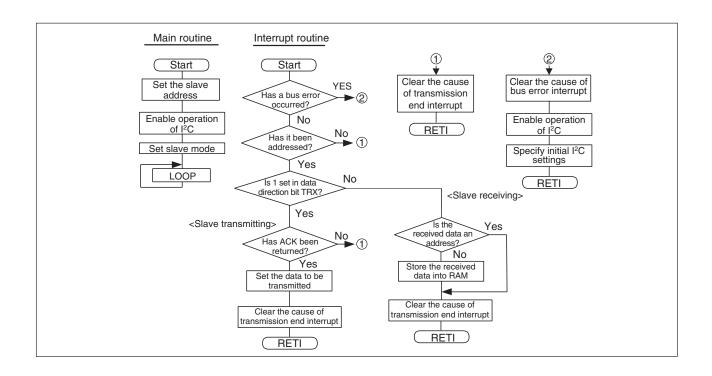

| 19.8 I <sup>2</sup> C Bus Interface Flowcharts             |     |

| 19.9 Program Example of the I <sup>2</sup> C Bus Interface |     |

|                                                            |     |

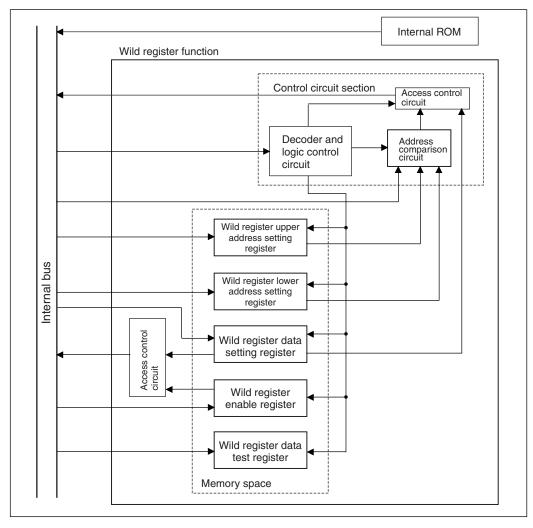

| CHAPTER 20 WILD REG          | ISTER FUNCTION                   | 475 |

|------------------------------|----------------------------------|-----|

| 20.1 Overview of the Wild R  | egister Function                 |     |

| 20.2 Configuration of the Wi | Id Register Function             |     |

| 20.3 Registers of the Wild R | egister Function                 |     |

| 20.3.1 Data Setting Registe  | ers (WRDR1 to WRDR6)             |     |

| 20.3.2 Upper Address Sett    | ing Registers (WRARH1 to WRARH6) |     |

| 20.3.3 Lower Address Sett    | ing Registers (WRARL1 to WRARL6) |     |

| 20.3.4 Wild Register Enabl   | e Register (WREN)                |     |

| 20.3.5 Wild Register Data    | Test Register (WROR)             |     |

| 20.4 Operation of the Wild F | Register Function                |     |

| 20.5 General Hardware Con    | nections                         |     |

| СНАРТЕ  | ER 21 CLOCK OUTPUT                                                                                               | 491      |

|---------|------------------------------------------------------------------------------------------------------------------|----------|

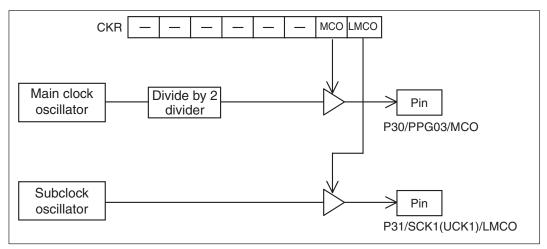

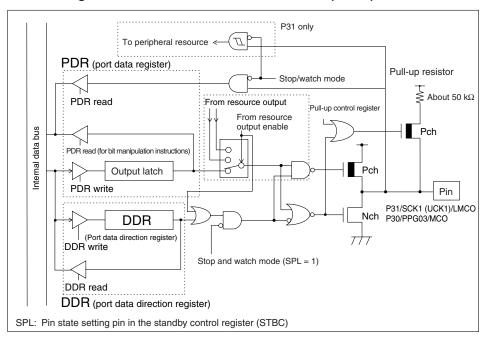

| 21.1 (  | Dverview of Clock Output                                                                                         | 492      |

| 21.2 (  | Clock Output Components                                                                                          | 493      |

| 21.3 (  | Clock Output Pins                                                                                                | 494      |

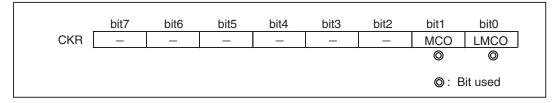

| 21.4 F  | Registers for Clock Output                                                                                       | 495      |

| 21.4.1  | 1 Clock Output Control Register (CKR)                                                                            | 496      |

| 21.5 E  | Description of Clock Output Operation                                                                            | 497      |

| 21.6 N  | Notes on Use of Clock Output                                                                                     | 498      |

| 21.7 \$ | Sample Clock Output Program                                                                                      | 499      |

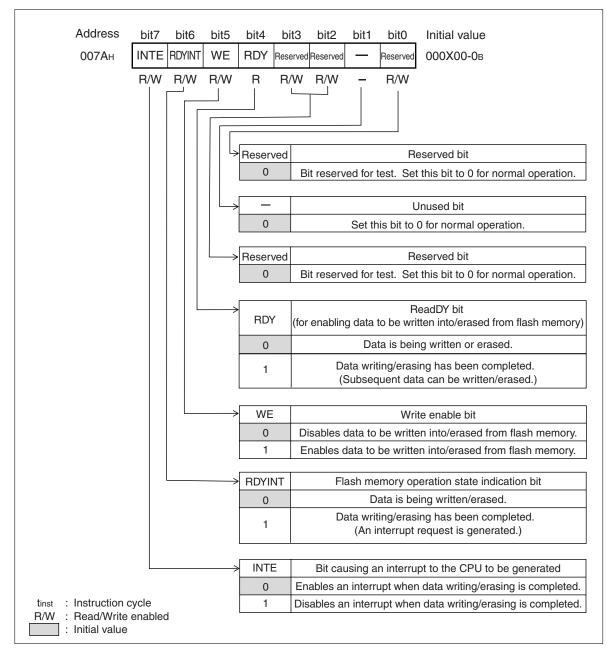

| СНАРТЕ  | ER 22 FLASH MEMORY                                                                                               | 501      |

| 22.1 (  | Dutline of Flash Memory                                                                                          | 502      |

|         | Sector Configuration of the Flash Memory                                                                         |          |

|         | Flash Memory Control Status Register (FMCS)                                                                      |          |

| 22.4 8  | Starting the Flash Memory Automatic Algorithm                                                                    | 506      |

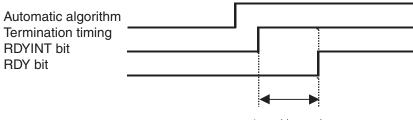

| 22.5 (  | Confirming the Automatic Algorithm Execution State                                                               | 507      |

| 22.5.1  | 1 Data Polling Flag (DQ7)                                                                                        | 509      |

| 22.5.2  | 2 Toggle Bit Flag (DQ6)                                                                                          | 510      |

| 22.5.3  | 3 Timing Limit Exceeded Flag (DQ5)                                                                               | 511      |

| 22.5.4  | 4 Sector Erase Timer Flag (DQ3)                                                                                  | 512      |

| 22.5.5  | 5 Toggle Bit-2 Flag (DQ2)                                                                                        | 513      |

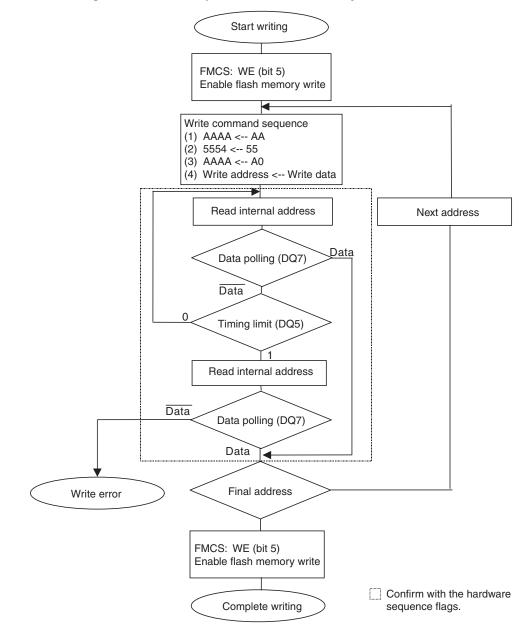

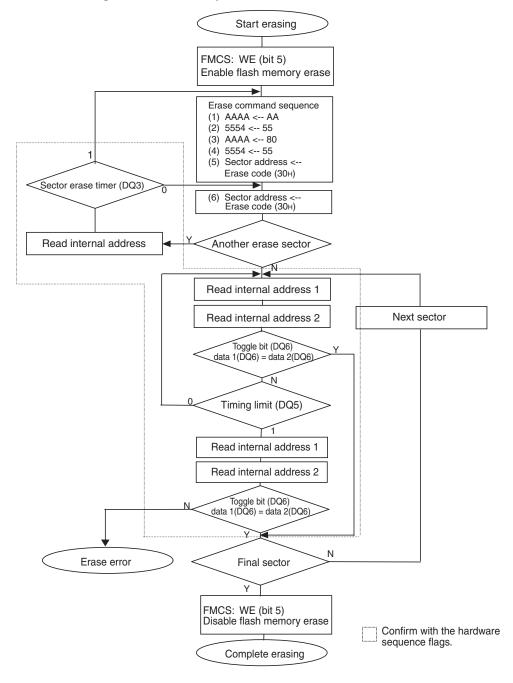

| 22.6 E  | Detailed Explanation of Writing to and Erasing Flash Memory                                                      | 514      |

| 22.6.1  | 1 Setting The Read/Reset State                                                                                   | 515      |

| 22.6.2  | 2 Writing Data                                                                                                   | 516      |

|         | 3 Erasing All Data (Erasing Chips)                                                                               |          |

|         | Erasing Data (Erasing Sectors)                                                                                   |          |

|         | 5 Suspending Sector Erase                                                                                        |          |

|         | 8 Restarting Sector Erase                                                                                        |          |

| 22.7 N  | Notes on using Flash Memory                                                                                      | 523      |

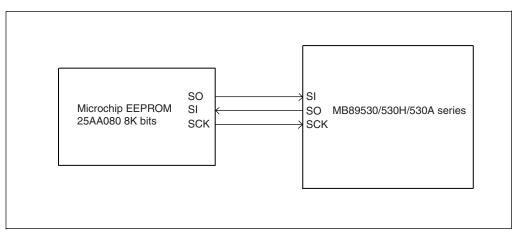

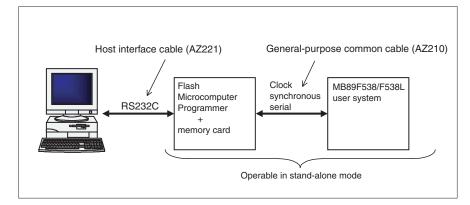

| СНАРТЕ  | ER 23 MB89F538/F538L SERIAL PROGRAMMING                                                                          | 525      |

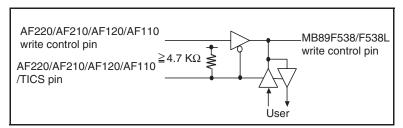

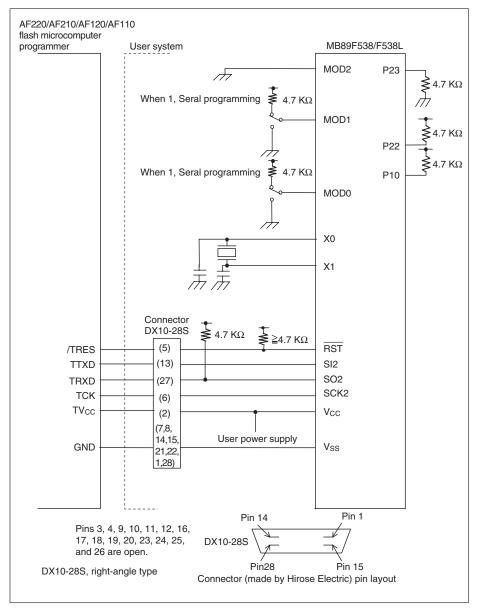

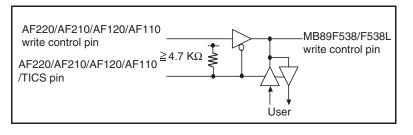

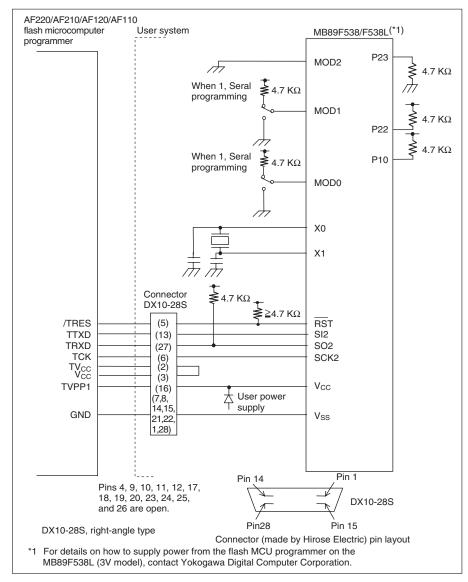

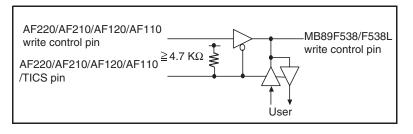

| 23.1 E  | Basic Configuration of MB89F538/F538L Serial Programming Connection                                              | 526      |

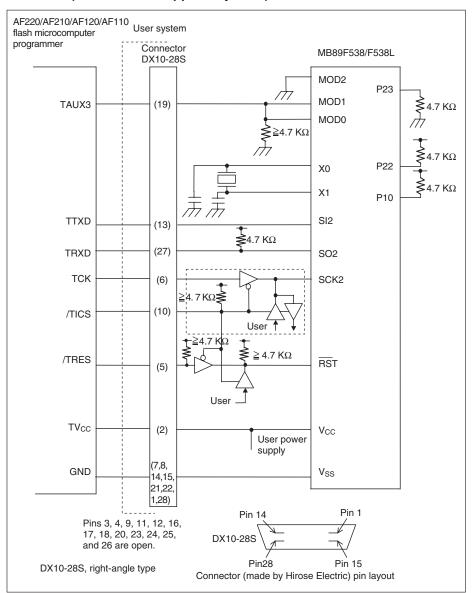

| 23.2 (  | Connection Example of Serial Programming (when User Power Supply is Used)                                        | 529      |

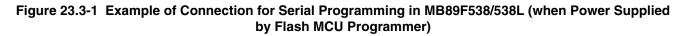

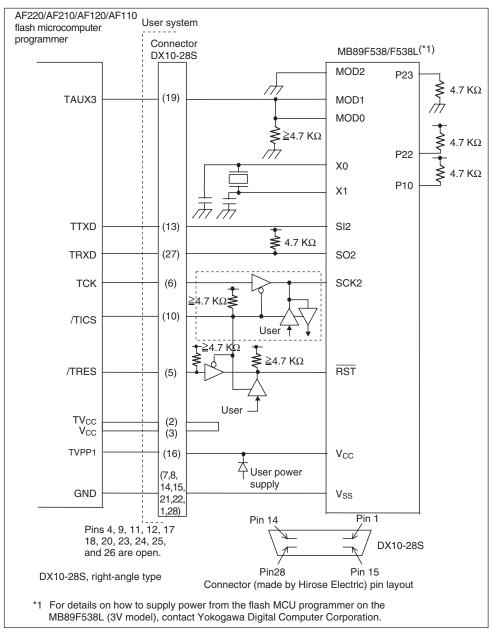

|         | Connection Example of Serial Programming (when Power Supply is Supplied from Flash MCU<br>Programmer)            | 531      |

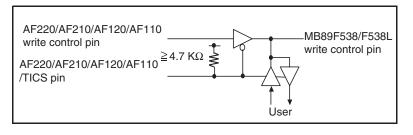

|         | Minimum Connection Example with Flash MCU Programmer (when User Power Supply is Use                              |          |

| 23.5 N  | Ainimum Connection Example with Flash Microcomputer Programmer (when Power Supply is S rom Flash MCU Programmer) | Supplied |

|         |                                                                                                                  |          |

|         | DIX                                                                                                              |          |

|         | IDIX A I/O Maps                                                                                                  |          |

|         | IDIX B Overview of Instructions                                                                                  |          |

| B.1     | Overview of F <sup>2</sup> MC-8L Instructions                                                                    |          |

| B.2     | Addressing                                                                                                       |          |

| B.3     | Special Instructions                                                                                             |          |

| B.4     | Bit Manipulation Instructions (SETB, CLRB)                                                                       |          |

| B.5     | F <sup>2</sup> MC-8L Instructions                                                                                |          |

| B.6     | Instruction Map                                                                                                  | 559      |

| INDEX                                                                         | 569 |

|-------------------------------------------------------------------------------|-----|

| APPENDIX G Troubleshooting                                                    | 566 |

| APPENDIX F Pin Statuses of the MB89530/530H/530A Series                       | 564 |

| APPENDIX E EPROM with Piggyback/Evaluation Chip                               | 563 |

| APPENDIX D Write Specifications for the One-Time PROM and EPROM Microcomputer | 561 |

| APPENDIX C Mask Options                                                       | 560 |

## CHAPTER 1 OVERVIEW

# This chapter describes the features and basic specifications of the MB89530/530H/ 530A series of microcontrollers.

- 1.1 "Features of the MB89530/530H/530A Series"

- 1.2 "Available Models of the MB89530/530H/530A Series"

- 1.3 "Differences among Models and the Precautions to Be Taken When Selecting Models"

- 1.4 "Block Diagram of the MB89530/530H/530A Series"

- 1.5 "Pin Layout"

- 1.6 "External Dimension Diagram"

- 1.7 "Explanations of the Pin Functions"

- 1.8 "I/O Circuit Format"

## 1.1 Features of the MB89530/530H/530A Series

The MB89530/530H/530A series is a one-chip microcontroller that uses the  $F^2MC^{\mbox{\ensuremath{\mathbb{R}}}}$ -8L core to support the low voltage and high-speed operation. The internal peripheral functions include the timers, serial interfaces, A/D converter, external interrupts, and so on. This series is a general-purpose one-chip microcontroller that is suitable for a broad range of uses, from consumer products to industrial equipment as well as for portable devices.

### Features of the MB89530/530H/530A series

### O Full package development

- Two types of QFP packages (1-mm pitch, 0.65-mm pitch)

- LQFP package (0.5-mm pitch)

- SH-DIP package

### **O** High-speed operation with low voltage

• Minimum instruction execution time 0.32 μs (for oscillation 12.5 MHz)

### ○ F<sup>2</sup>MC<sup>®</sup>-8L CPU core

Optimal instruction system for the controller

- Multiplication and division instructions

- 16-bit arithmetic operations

- Branch instructions with bit test

- Bit manipulation instructions

### O Five-system timer

- 8-bit PWM timer: 2-channel timer (can be used as the interval timer or PWM timer)

- Pulse-width count timer (supports the usages such as continuous measurement and remote control reception)

- 16-bit timer counter

- 21-bit timebase timer

- Watch prescaler (17 bits)

### O UART

• Clock synchronization and asynchronization can be switched.

### • Two serial interfaces (serial I/O)

• Transfer direction can be selected (specification of MSB first or LSB first), enabling communication with a variety of devices.

### ○ 10-bit A/D converter (8 channels)

The start of the A/D converter is supported with external clock input and timebase timer output. (The A/D converter cannot be started with external clock input for MB89F538/ F538L.)

### **O** Two programmable pulse generators (PPGs)

- 6-bit PPG that enables a pulse width and cycle to be selected with a program

- 12-bit PPG that enables a pulse width and cycle to be selected with a program (2 channels)

### ○ I<sup>2</sup>C interface circuit

- O External interrupt 1 (single-clock system product: 4 channels, dual-clock system product: 3 channels)

- Four or three inputs are independent, enabling releases from standby mode. (With the edge detection function)

# O External interrupt 2 (product other than MB89F538/F538L: 8 channels, MB89F538/F538L: 7 channels)

• Eight or seven inputs are independent, enabling releases from standby mode. (With the level edge detection function)

### **O** Standby mode (low-power consumption mode)

- Stop mode (current consumption hardly takes place because oscillation stops)

- Sleep mode (current consumption becomes about 1/3 of the usual amount because the CPU stops)

- Subclock mode

- Watch mode

### **O** Watchdog timer reset

### O I/O ports

- Maximum number of ports

- Single-clock system product

Other than MB89F538/F538L: 53 ports

MB89F538/F538L: 52 ports

Dual-clock system product

Other than MB89F538/F538L: 51 ports

MB89F538/F538L: 50 ports

### CHAPTER 1 OVERVIEW

- General-purpose I/O port (CMOS)

Other than MB89F538/F538L: 38 ports

MB89F538/F538L: 37 ports

- General-purpose I/O port (N-channel open drain): 2 ports

- General-purpose output port (N-channel open drain): 8 ports

- General-purpose input port (CMOS)

Single-clock system product: 5 ports

- Dual-clock system product: 3 ports

## 1.2 Available Models of the MB89530/530H/530A Series

Four models of the MB89530/530H/530A series are supported. Table 1.2-1 "Available models of the MB89530/530H/530A series" lists the available models and Table 1.2-2 "CPU and peripheral functions of the MB89530/530H/530A series" lists the CPU and peripheral functions.

■ Available models of the MB89530/530H/530A series

| Table 1.2-1 | Available models of the MB89530/530H/530A series |

|-------------|--------------------------------------------------|

|-------------|--------------------------------------------------|

|                      | Model                                                                                                                                                                             |                                                  |                                                                                                                                 |                                           |                                   |                                          |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------|------------------------------------------|

| Item                 | MB89535A                                                                                                                                                                          | MB89537/537C<br>MB89537H/537HC<br>MB89537A/537AC | MB89538/538C<br>MB89538H/538HC<br>MB89538A/538AC                                                                                | MB89F538/F538L                            | MB89P538                          | MB89PV530                                |

| Classification       | Mass production (mask ROM product)                                                                                                                                                |                                                  |                                                                                                                                 | Flash Memory                              | PROM                              | EVA                                      |

| ROM<br>capacity      | 16 KB x 8 bits<br>(Internal ROM)                                                                                                                                                  | 32 KB x 8 bits<br>(Internal ROM)                 | 48 KB x 8 bits<br>(Internal ROM)                                                                                                | 48 KB x 8 bits<br>(Internal flash memory) | 48 KB x 8 bits<br>(Internal PROM) | 48 KB x 8 bits<br>(External ROM)<br>(*2) |

| RAM<br>capacity      | 512 x 8 bits                                                                                                                                                                      | 1 KB x 8 bits                                    | 2 KB x 8 bits                                                                                                                   |                                           |                                   |                                          |

| Operating<br>voltage | 2.2V to 3.6V <sup>(*1)</sup> (MB89537/538/537C/538C)<br>3.5V to 5.5V <sup>(*1)</sup> (MB89537H/538H/537HC/538HC)<br>2.2V to 5.5V <sup>(*1)</sup> (MB89535A/537A/538A/537AC/538AC) |                                                  | MB89F538:<br>3.5V to 5.5V <sup>(*1)</sup><br>MB89F538L:<br>2.4V to 3.6V <sup>(*1)(*3)</sup><br>2.7V to 3.6V <sup>(*1)(*4)</sup> | 2.7V t                                    | o 5.5V                            |                                          |

\*1 Depends on the operating frequency.

\*2 MBM27C512 is used as the external ROM.

\*3 Flash memory read assurance voltage.

\*4 Flash memory read/write assurance voltage.

Note:

MB89537/538/537H/538H/535A/537A/538A contain no I<sup>2</sup>C function.

To use the I<sup>2</sup>C function, use MB89PV530/MB89P538/MB89F538/MB89F538L/MB89537C/538C/537HC/ 538HC/537AC/538AC.

| Item            |                   | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                        |  |  |

|-----------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| CPU function    |                   | Number of basic instructions<br>Instruction bit length<br>Instruction length<br>Data bit length<br>Minimum instruction execution time<br>Minimum interrupt processing time                                                                                                                                                                                                                                                                                  | : 136<br>: 8 bits<br>: 1 to 3 bytes<br>: 1, 8, and 16 bits<br>: 0.32 μs/12.5 MHz<br>: 2.88 μs/12.5 MHz |  |  |

|                 |                   | Input port                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                        |  |  |

|                 | Port              | Single-clock system product                                                                                                                                                                                                                                                                                                                                                                                                                                 | : 5 ports (Four ports also serve as external interrupts.)                                              |  |  |

|                 |                   | Dual-clock system product                                                                                                                                                                                                                                                                                                                                                                                                                                   | : 3 ports (Three ports also serve as external interrupts.)                                             |  |  |

|                 |                   | Output-dedicated port (N-channel)                                                                                                                                                                                                                                                                                                                                                                                                                           | : 8 ports (Eight ports are also used as ADC input.)                                                    |  |  |

|                 |                   | I/O port<br>(N-channel open drain)                                                                                                                                                                                                                                                                                                                                                                                                                          | : 2 ports (Two ports also serve as S02/<br>SDA and SI2/SCL.)                                           |  |  |

|                 |                   | I/O port (CMOS)                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                        |  |  |

|                 |                   | Other than MB89F538/F538L                                                                                                                                                                                                                                                                                                                                                                                                                                   | : 38 pins                                                                                              |  |  |

|                 |                   | • MB89F538/F538L                                                                                                                                                                                                                                                                                                                                                                                                                                            | : 37 pins (Twenty-one ports do not serve as other functions.)                                          |  |  |

| Peripheral      |                   | Total                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                        |  |  |

| function        |                   | Single-clock system product                                                                                                                                                                                                                                                                                                                                                                                                                                 | Other than MB89F538/F538L: 53 ports<br>MB89F538/F538L: 52 ports                                        |  |  |

|                 |                   | Dual-clock system product                                                                                                                                                                                                                                                                                                                                                                                                                                   | Other than MB89F538/F538L: 51 ports<br>MB89F538/F538L: 50 ports                                        |  |  |

|                 | Timebase<br>timer | 21 bits<br>Interrupt cycle for main clock original oscillation 12.5 MHz (approx. 0.655 ms,<br>2.621 ms, 20.97 ms, and 335.5 ms)                                                                                                                                                                                                                                                                                                                             |                                                                                                        |  |  |

|                 | Watchdog<br>timer | Reset cycle for main clock original oscillation 12.5 MHz (approx. 167.8 to 335.6 ms)<br>Reset cycle for subclock original oscillation 32.768 KHz (approx. 500 to 1,000 ms)                                                                                                                                                                                                                                                                                  |                                                                                                        |  |  |

|                 | PWM timer         | <ul> <li>8-bit interval timer operation<br/>(Rectangular output supported, operating clock cycle: 1t<sub>inst</sub>, 8t<sub>inst</sub>, 16t<sub>inst</sub>, and 64t<sub>inst</sub>)</li> <li>8-bit resolution pulse width measurement (conversion cycle: 2<sup>8</sup>t<sub>inst</sub> to 2<sup>8</sup> x 64t<sub>inst</sub>)</li> <li>2 channels (also usable as the interval timer), usable as the channel 1 output and channel 2 count clock.</li> </ul> |                                                                                                        |  |  |

| Watch prescaler |                   | Interval time for 17-bit subclock original oscillation 32.768 KHz<br>(Approx. 31.25 ms, 0.25 s, 0.50 s, 1.00 s, 2.00 s, and 4.00 s)                                                                                                                                                                                                                                                                                                                         |                                                                                                        |  |  |

Table 1.2-2 CPU and peripheral functions of the MB89530/530H/530A series

| ltem                             |                                   | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|----------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                  | Pulse<br>width<br>count timer     | $\begin{array}{l} \text{8-bit one-shot timer operation} \\ (\text{Underflow output supported, operating clock cycle: } 1t_{inst}, 4t_{inst}, 32t_{inst}, \text{ and} \\ \text{external}) \\ \text{8-bit reload timer operation (rectangular output supported, operating clock cycle: } 1t_{inst}, 4t_{inst}, 32t_{inst}, \text{ and external}) \\ 8-bit pulse width measurement operation (the following measurements are possible: continuous measurement, H width measurement, L width measurement, measurement from \uparrow to \uparrow, measurement from \downarrow to \downarrow, and both H width measurement and measurement from \uparrow to \uparrow)$ |  |  |  |

|                                  | 16-bit<br>timer/<br>counter       | 16-bit timer operation (operating clock cycle: 1t <sub>inst</sub> , and external)<br>16-bit event counter operation (rising edge, falling edge, or both selectable)<br>16 bits x 1 channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                  | Serial I/O                        | 8-bit length<br>LSB or MSB precedence selectable<br>Transfer clock (2t <sub>inst</sub> , 8t <sub>inst</sub> , 32t <sub>inst</sub> , and external)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

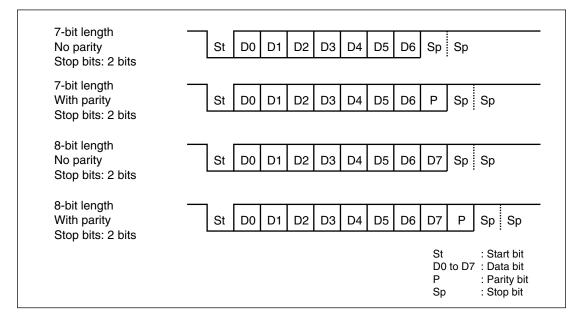

| Peripheral<br>functions          | UART/SIO                          | CLK synchronization/CLK asynchronization data transferable (bits 8 and 9 with parity bits, bits 7 and 8 without parity bits)<br>14 baud rates can be selected with the internal baud rate generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

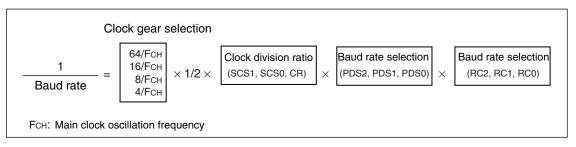

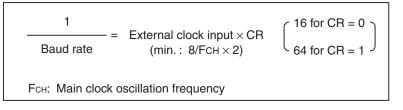

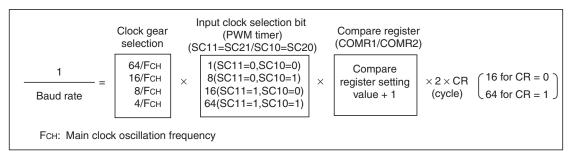

|                                  | UART                              | CLK synchronization/CLK asynchronization data transferable (bits 4, 6, 7, and 8<br>with parity bits, bits 5, 7, 8, and 9 without parity bits)<br>14 baud rates can be selected with the internal baud rate generator.<br>Baud rates can also be set with external clock input and 2-channel 8-bit PWM<br>timer output.                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                  | External<br>interrupt 1           | Single-clock system product: independent 4 channels, dual-clock system product:<br>independent 3 channels<br>Rising edge, falling edge, or both can be selected.<br>Usable for release from standby mode (edge detection can also be used in stop<br>mode).                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                  | External<br>interrupt 2           | Other than MB89F538/F538L: independent 8 channel L level detection,<br>MB89F538/F538L: independent 7 channel L level detection<br>Usable for release from standby mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                  | 6-bit PPG,<br>12-bit PPG          | Rectangular waves whose cycle is programmable can be generated.<br>6 bits x 1 channel and 12 bits x 2 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                  | I <sup>2</sup> C bus<br>interface | 1 channel, conforms to the system management bus revised edition 1.0 of the<br>Intel Corporation and to the I <sup>2</sup> C specifications of Philips Electronics.<br>2-wire system communication (contained only in the following: MB89PV530/P538/<br>F538/F538L/537C/538C/537HC/538HC/537AC/538AC)                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                  | A/D<br>converter                  | 10-bit resolution x 8 channels<br>A/D conversion function (conversion time: 60t <sub>inst</sub> )<br>Repeated start is supported with external or internal clocks (MB89F538/<br>MB89F538L is excluded from repeated start with external clocks.)<br>Reference voltage input available (AVR)                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Standby mode<br>(low-power mode) |                                   | Sleep mode, stop mode, subclock mode, and watch mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Process                          |                                   | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

$t_{inst}$ : Instruction cycle (execution time). 1/4, 1/8, 1/16, or 1/64 of the main clock or 1/2 of the subclock can be selected (see Section 3.6 "Clock").

### 1.3 Differences among Models and the Precautions to Be Taken When Selecting Models

This section describes the differences among five models of the MB89530/530H/530A series and the precautions to be taken when selecting models.

■ Differences among models and precautions to be taken when selecting models

Table 1.3-1 Packages of the supported models

|             | Model    |                                                  |                                                  |                                   |           |  |

|-------------|----------|--------------------------------------------------|--------------------------------------------------|-----------------------------------|-----------|--|

| Package     | MB89535A | MB89537/537C<br>MB89537H/537HC<br>MB89537A/537AC | MB89538/538C<br>MB89538H/538HC<br>MB89538A/538AC | MB89P538<br>MB89F538<br>MB89F538L | MB89PV530 |  |

| DIP-64P-M01 | 0        | 0                                                | 0                                                | 0                                 | х         |  |

| FPT-64P-M03 | 0        | 0                                                | 0                                                | х                                 | х         |  |

| FPT-64P-M06 | 0        | 0                                                | 0                                                | 0                                 | x         |  |

| FPT-64P-M09 | 0        | 0                                                | 0                                                | 0                                 | х         |  |

| MDP-64C-P02 | х        | х                                                | х                                                | х                                 | 0         |  |

| MQP-64C-P01 | х        | х                                                | х                                                | х                                 | 0         |  |

[o]: Usable

[x]: Unusable

The conversion socket (manufactured by Sunhayato Corporation) can be used to convert a pin pitch. Where to make contact: Sunhayato Corporation

Tel. 03-3986-0403

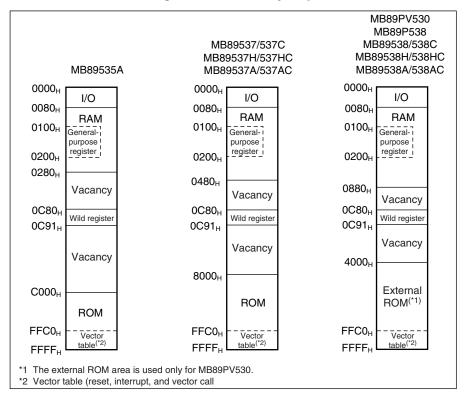

### O Memory space

To use a piggyback model for evaluation, carefully confirm the differences between this model and the model to be actually used. Pay special attention to the following points. (See Section 3.1 "Memory Space.")

- The program ROM area begins from 4000H on MB89P538, MB89F538, MB89F538L, and MB89PV530.

- The stack area is set in the upper limit of the RAM

### ○ Current consumption

- For MB89PV530, the current consumed by EPROM connected to the top socket is added.

- During low-speed operation, the current consumption of the model mounted on the one-time PROM or the EPROM is greater than that of the model mounted on the mask ROM. However, the current consumption in sleep or stop mode is equal for both cases.

For details, see the electrical characteristics of the data sheet.

### 1.3 Differences among Models and the Precautions to Be Taken When Selecting Models

### O Mask option

The functions that can be specified with options and the method of specifying the options depend on the model. Before using the options, first refer to Appendix C "Mask Options" for details.

### **O** Wild register function

Table 1.3-2 "Spaces in which the wild register function can be used" lists the spaces in which the wild register function can be used.

### Table 1.3-2 Spaces in which the wild register function can be used

| Model name                         | Address space                          |

|------------------------------------|----------------------------------------|

| MB89PV530                          | 4000 <sub>H</sub> to FFFF <sub>H</sub> |

| MB89P538/F538/F538L                | 4000 <sub>H</sub> to FFFF <sub>H</sub> |

| MB89537/537C/537H/537HC/537A/537AC | 8000 <sub>H</sub> to FFFF <sub>H</sub> |

| MB89538/538C/538H/538HC/538A/538AC | 4000 <sub>H</sub> to FFFF <sub>H</sub> |

| MB89535A                           | C000 <sub>H</sub> to FFFF <sub>H</sub> |

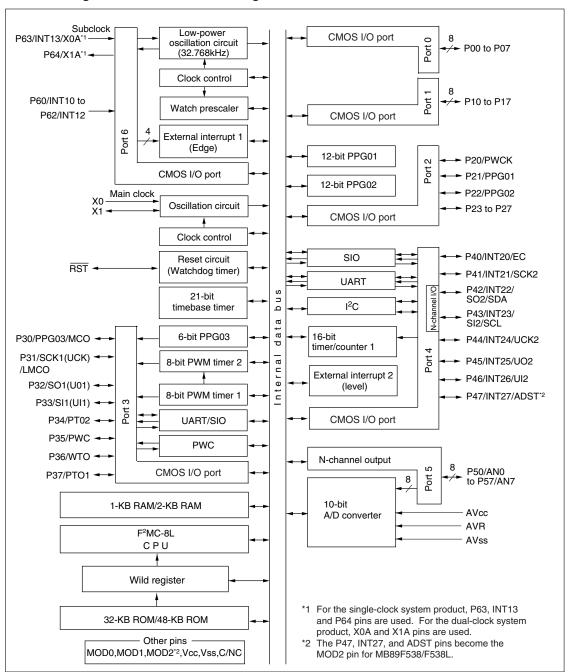

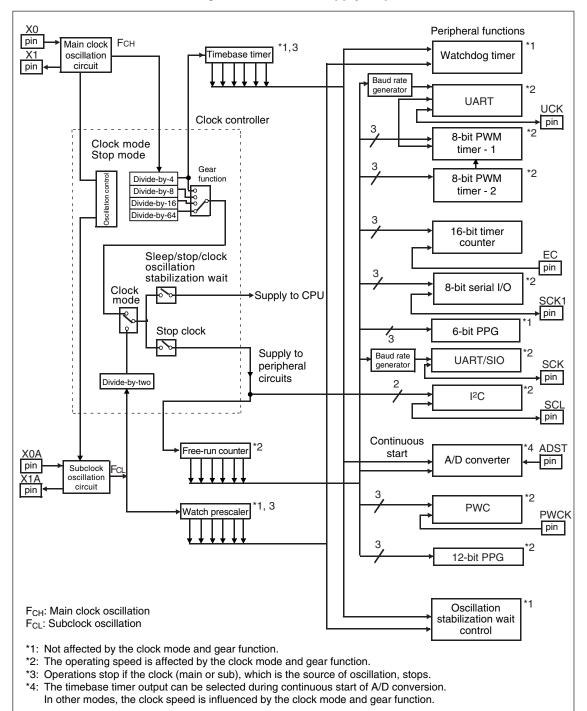

## 1.4 Block Diagram of the MB89530/530H/530A Series

Figure 1.4-1 "Entire block diagram of the MB89530/530H/530A series" shows the block diagram of the MB89530/530H/530A series.

■ Entire block diagram of the MB89530/530H/530A series

Figure 1.4-1 Entire block diagram of the MB89530/530H/530A series

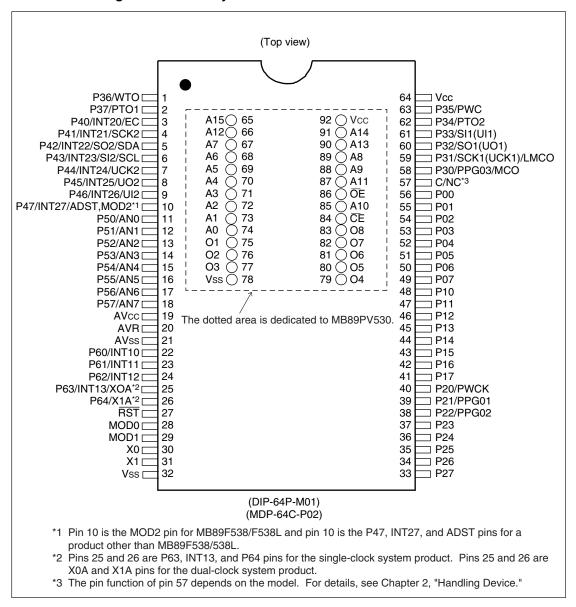

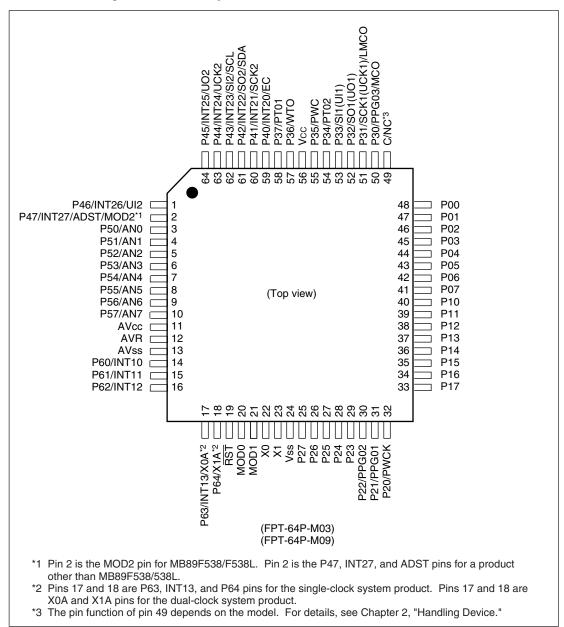

### 1.5 Pin Layout

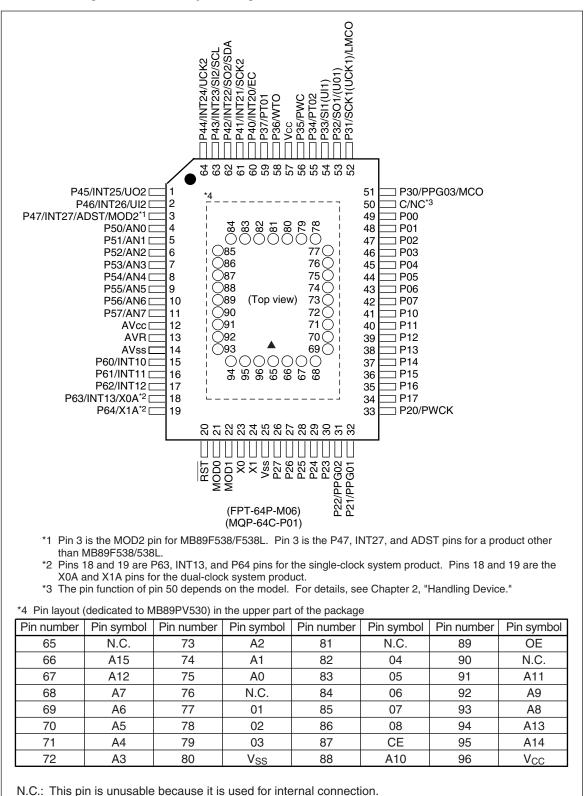

Figure 1.5-1 "Pin layout for DIP-64P-M01 and MDP-64C-P02", Figure 1.5-2 "Pin layout for FPT-64P-M03 and FPT-64P-M09", and Figure 1.5-3 "Pin layout diagram for FPT-64P-M06 and MQP-64C-P01" show the pin layouts of the MB89530/530H/530A series.

■ Pin layout for DIP-64P-M01 and MDP-64C-P02

Figure 1.5-1 Pin layout for DIP-64P-M01 and MDP-64C-P02

### ■ Pin layout for FPT-64P-M03 and FPT-64P-M09

Figure 1.5-2 Pin layout for FPT-64P-M03 and FPT-64P-M09

Figure 1.5-3 Pin layout diagram for FPT-64P-M06 and MQP-64C-P01

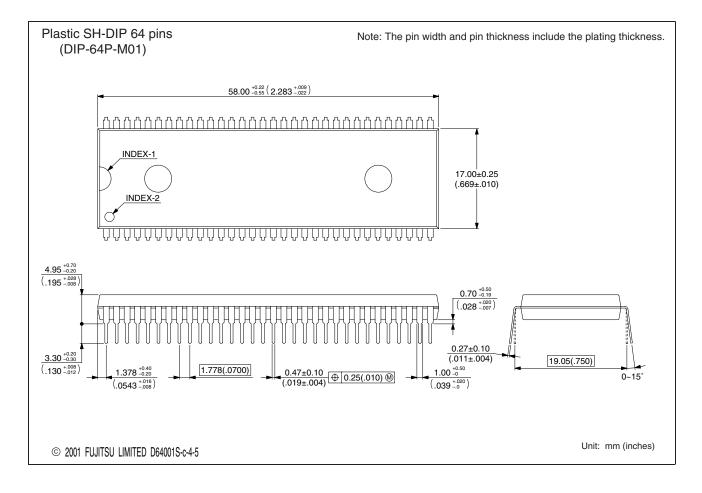

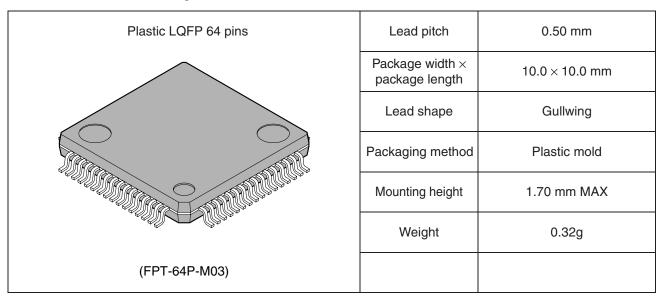

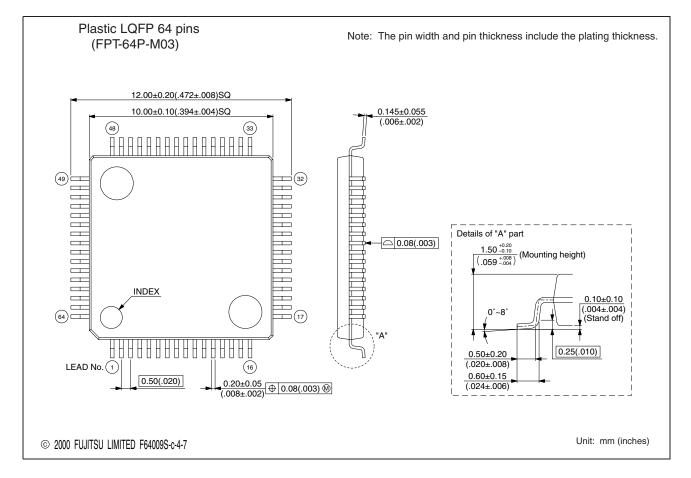

## 1.6 External Dimension Diagram

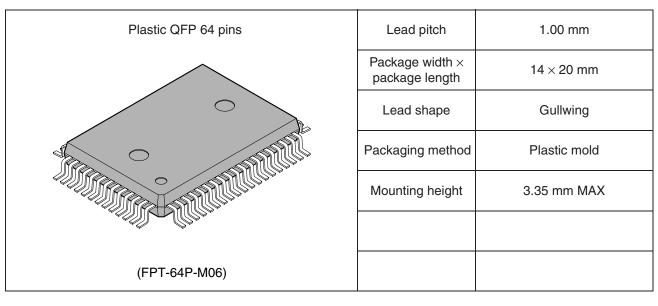

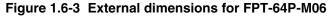

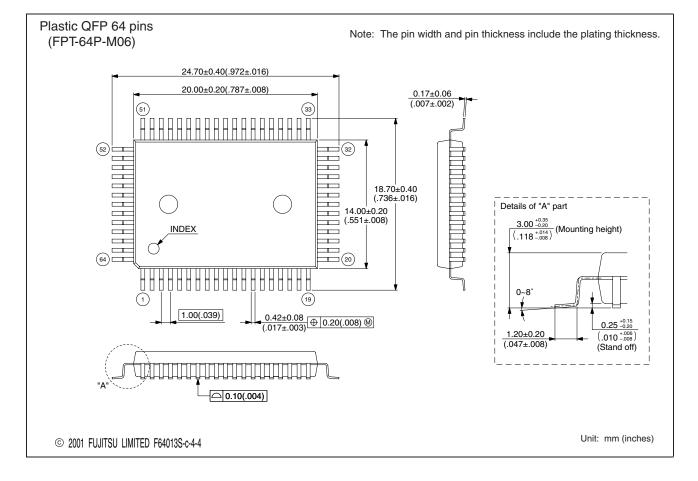

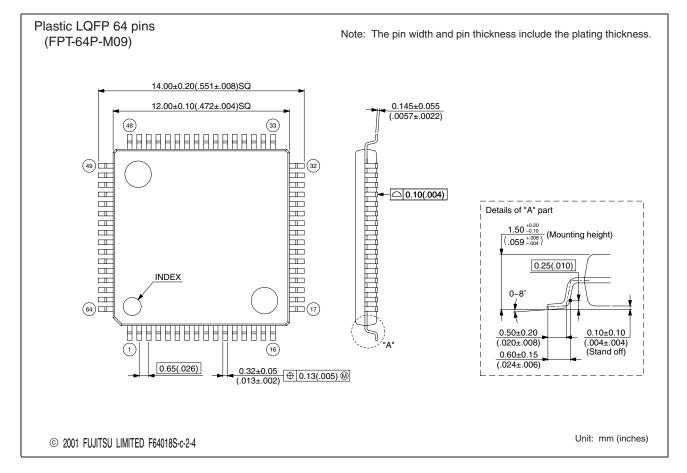

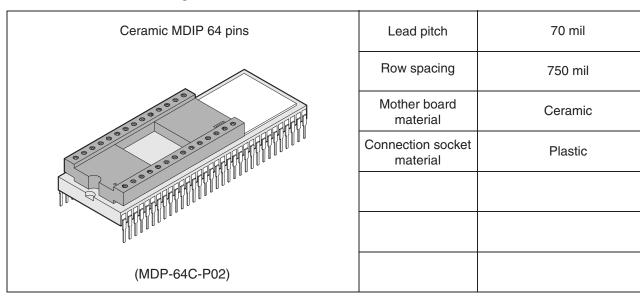

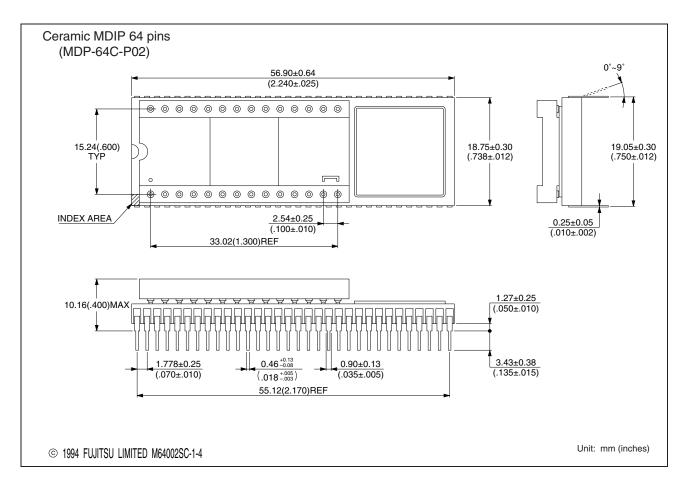

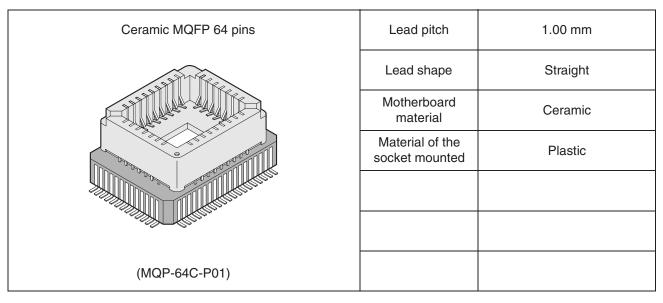

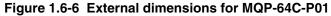

Six packages are provided for the MB89530/530H/530A series. Figure 1.6-1 "External dimensions for DIP-64P-M01" to Figure 1.6-6 "External dimensions for MQP-64C-P01" show their external dimensions.

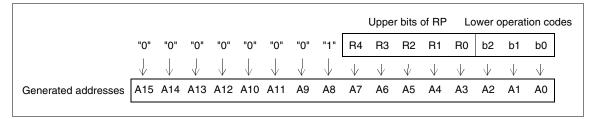

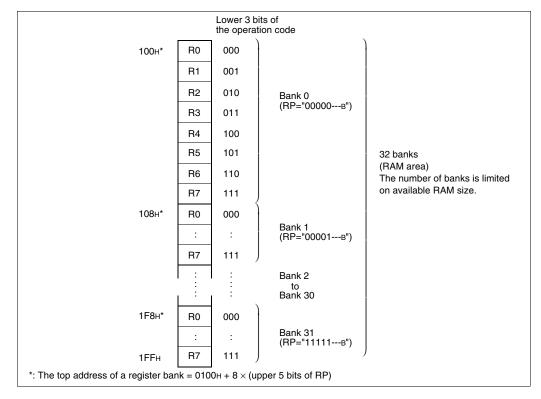

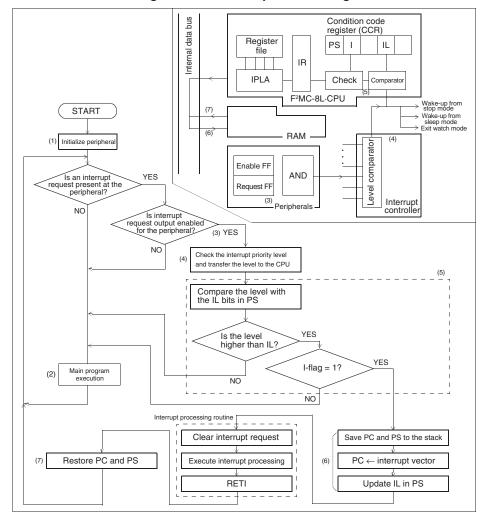

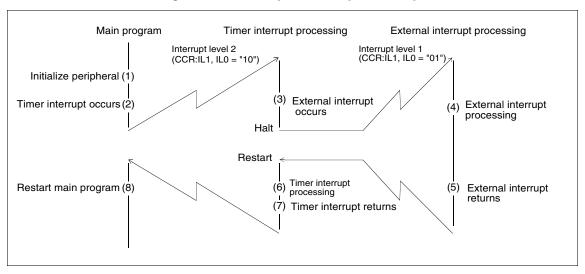

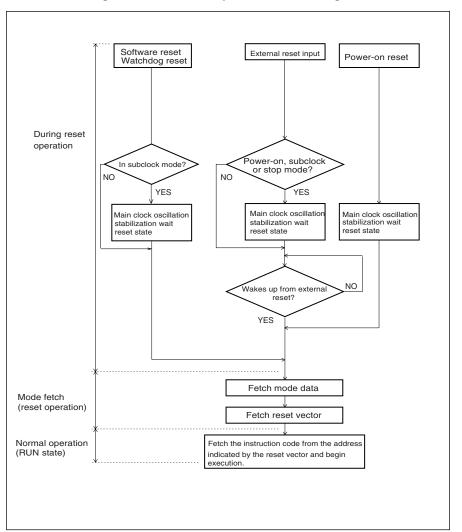

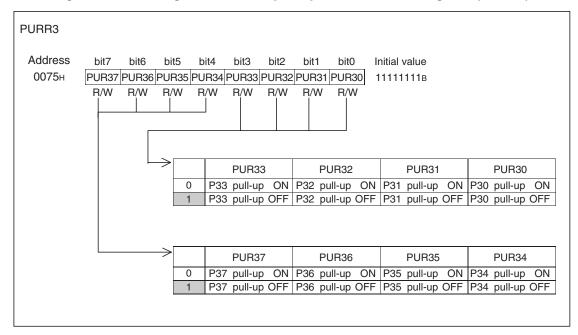

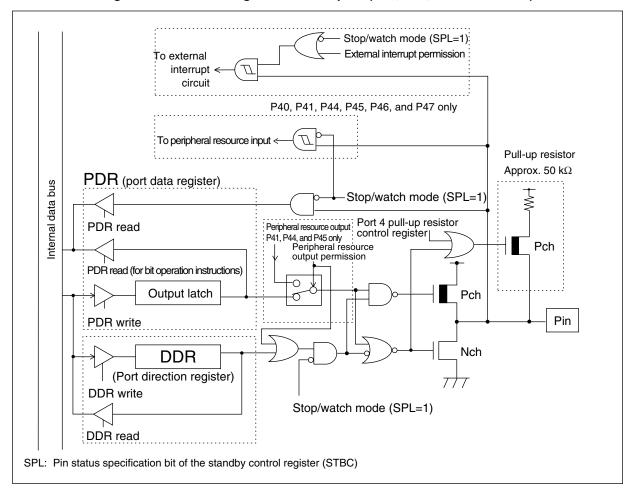

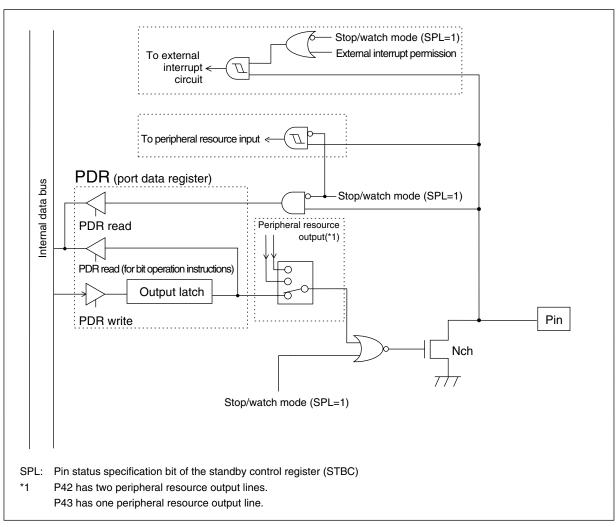

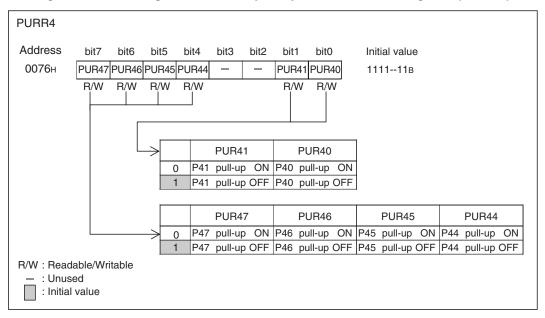

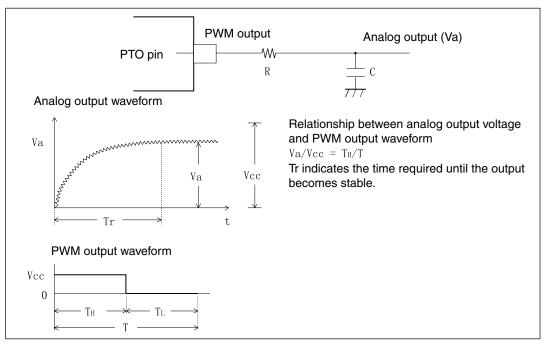

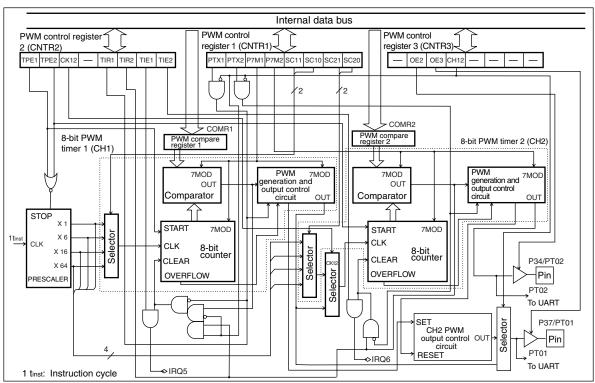

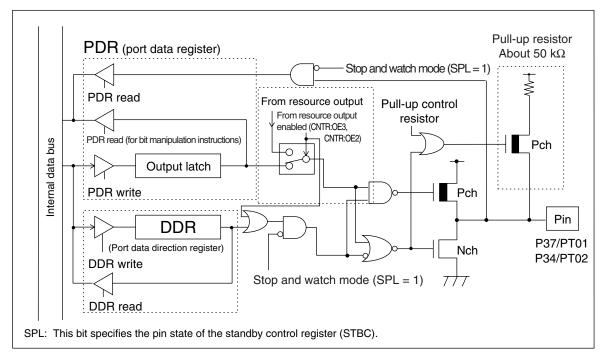

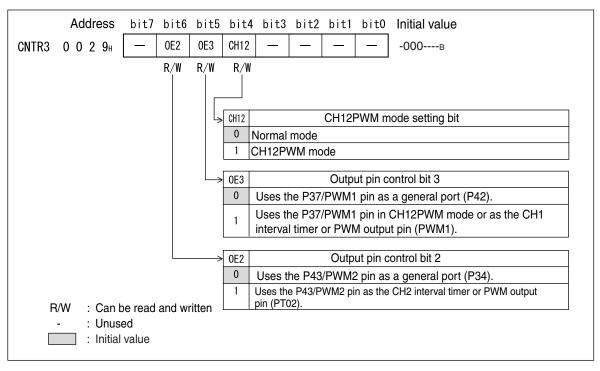

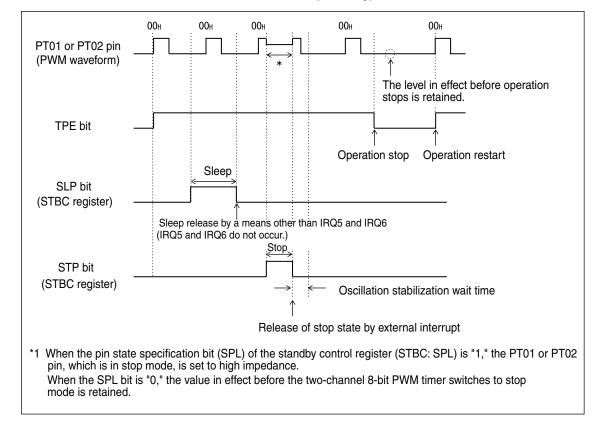

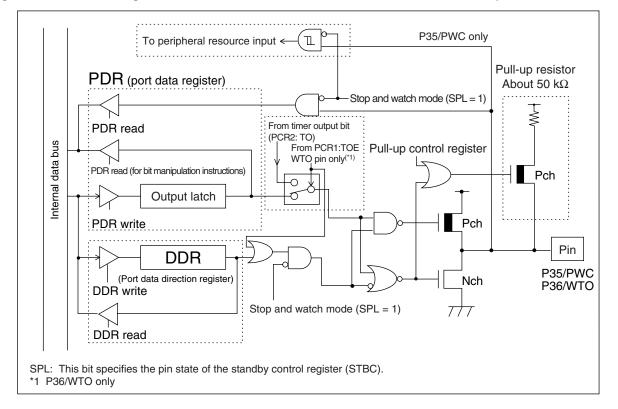

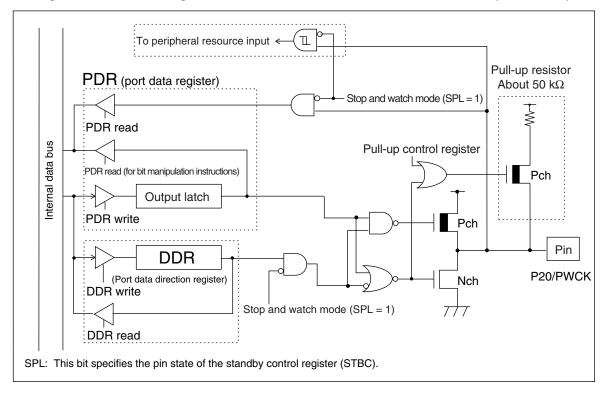

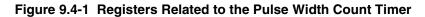

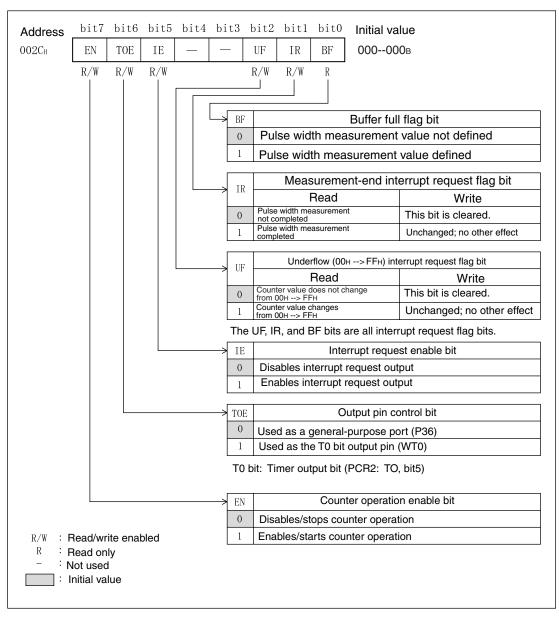

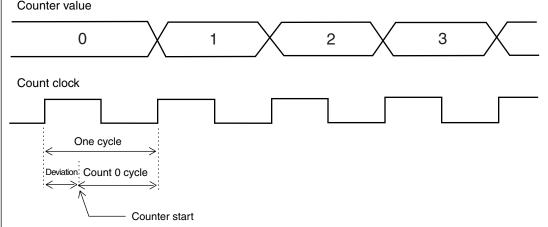

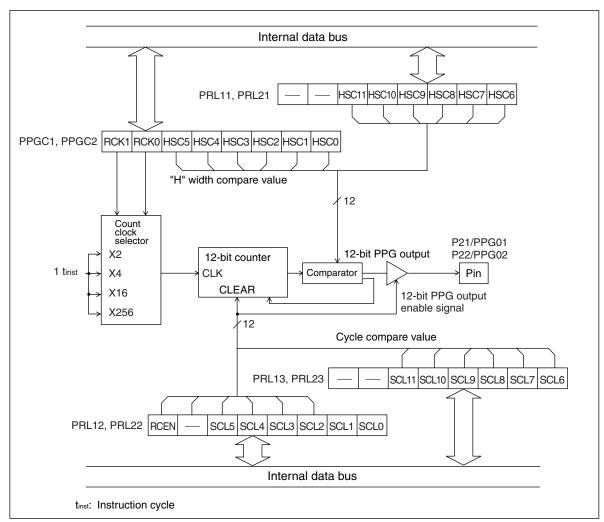

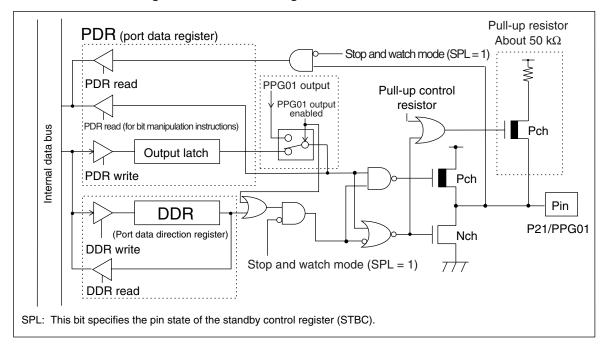

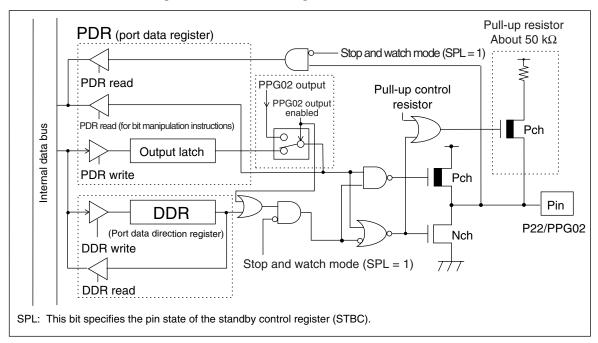

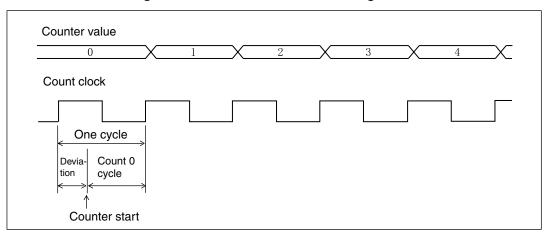

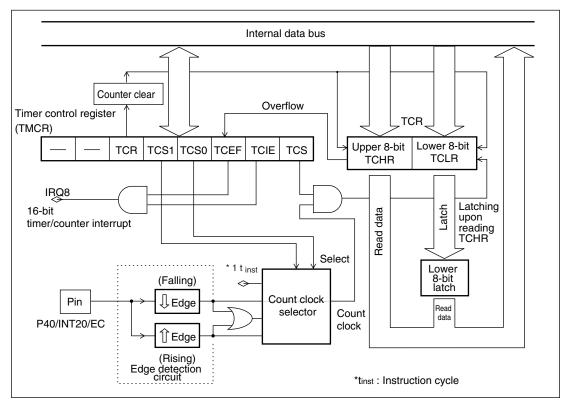

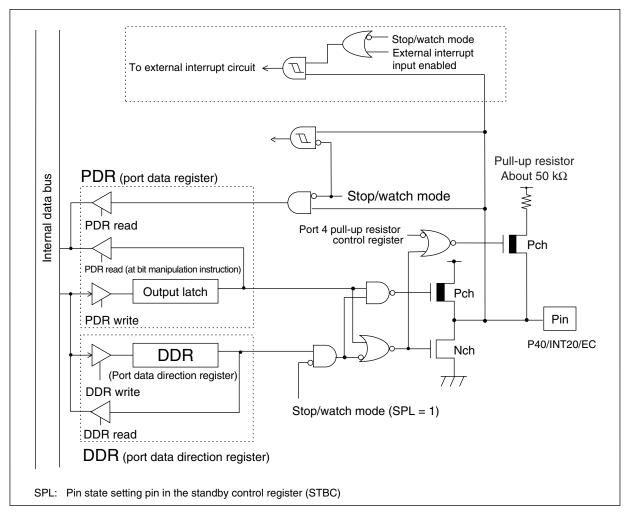

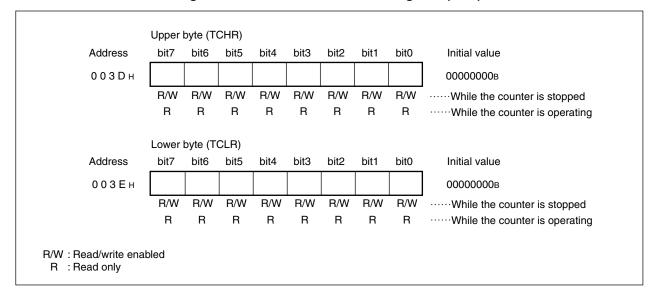

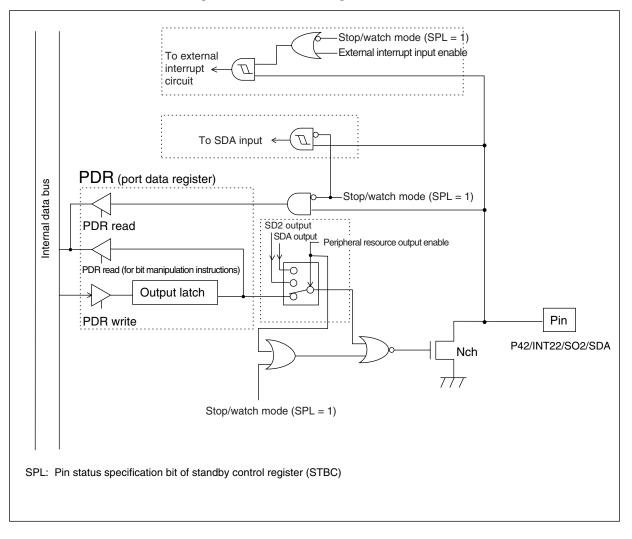

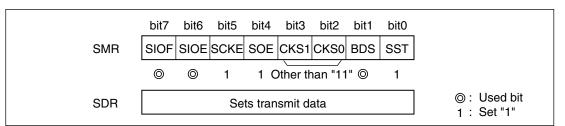

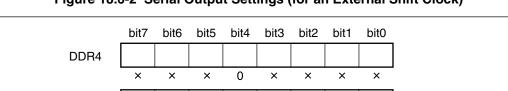

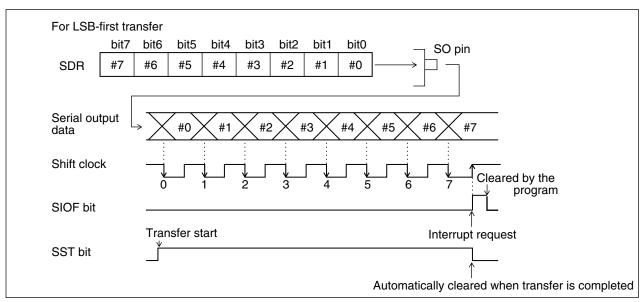

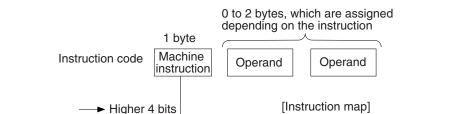

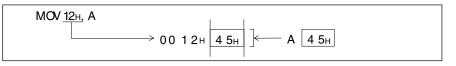

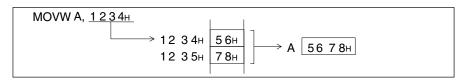

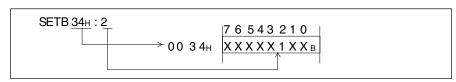

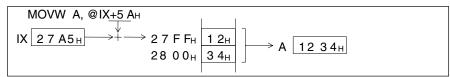

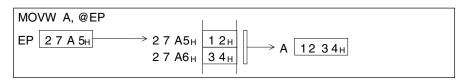

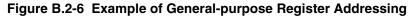

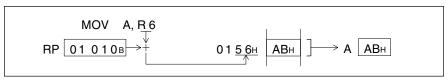

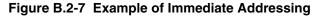

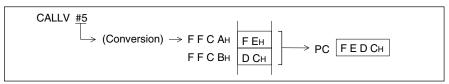

| Plastic SH-DIP 64 pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Lead pitcl                 |